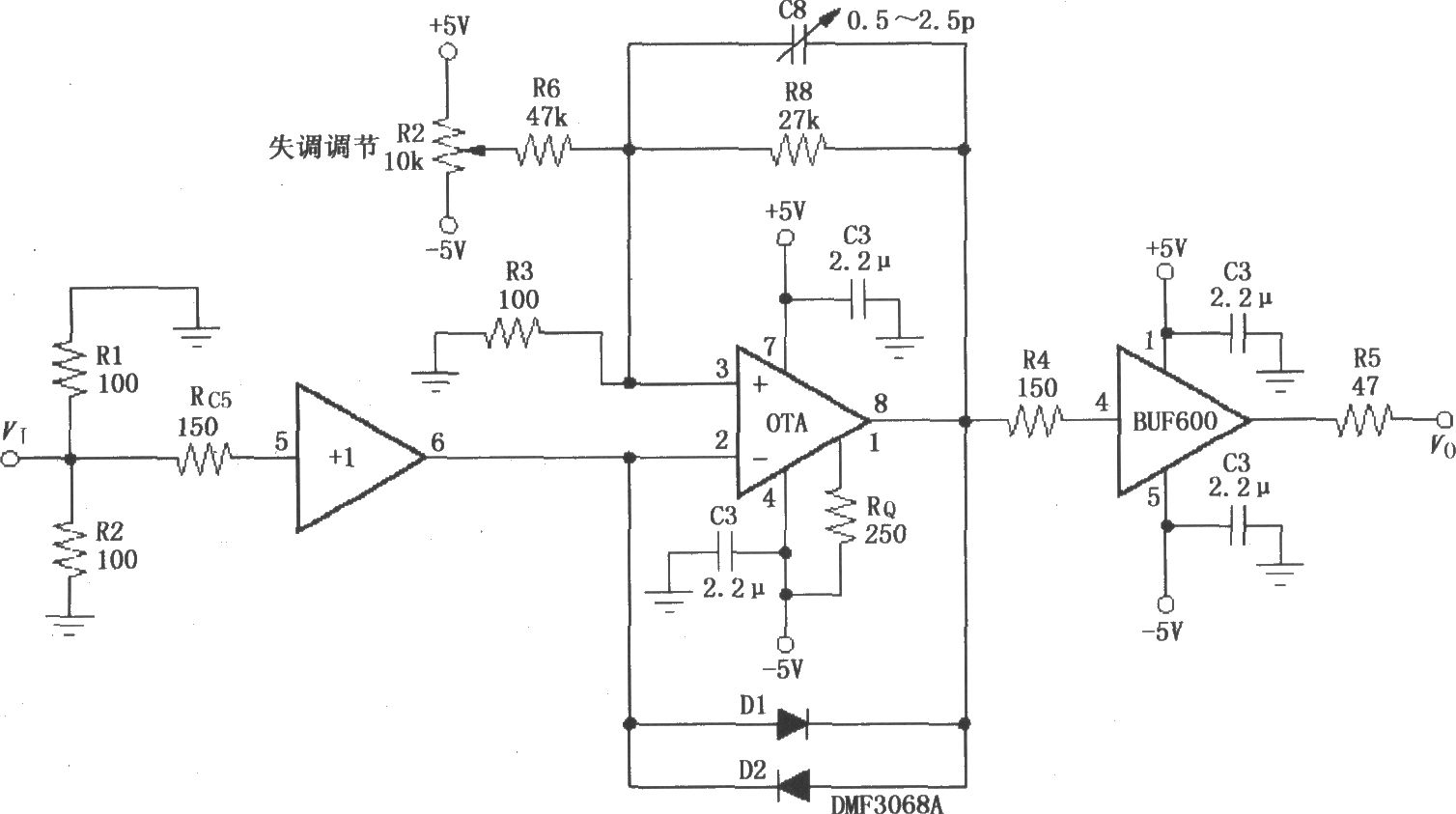

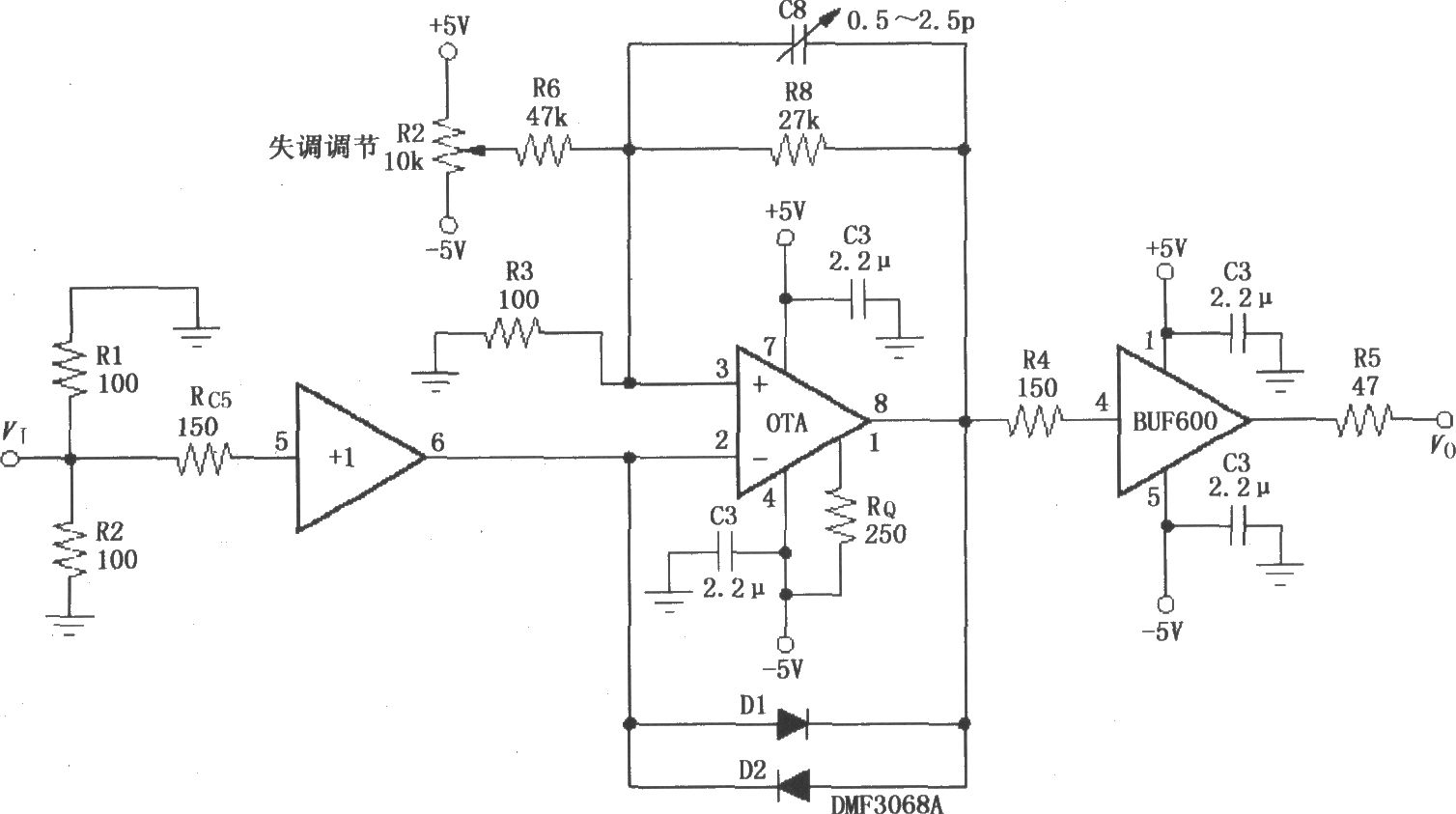

如圖所示為由OPA660與緩沖放大器BUF600構成的比較(低抖動)電路。比較器電路的基準電壓由電位器R2設定(R2也可用于失調調節),信號電壓VI經過150Ω電阻加到OPA660內部 1放大器輸入端5腳,由 1放大器6腳輸出到OTA的2腳。2腳與3腳兩個信號比較,當2腳電壓>3腳電壓時,OPA660輸出端8腳為高電平;反之,當2腳電壓<3腳電壓時,OPA660輸出端8腳為低電平。OPA660輸出端8腳信號再經過緩沖放大器BUF600輸出。傳輸延時時間為5nS;上升時間為1.5ns。

如圖所示為由OPA660與緩沖放大器BUF600構成的比較(低抖動)電路。比較器電路的基準電壓由電位器R2設定(R2也可用于失調調節),信號電壓VI經過150Ω電阻加到OPA660內部 1放大器輸入端5腳,由 1放大器6腳輸出到OTA的2腳。2腳與3腳兩個信號比較,當2腳電壓>3腳電壓時,OPA660輸出端8腳為高電平;反之,當2腳電壓<3腳電壓時,OPA660輸出端8腳為低電平。OPA660輸出端8腳信號再經過緩沖放大器BUF600輸出。傳輸延時時間為5nS;上升時間為1.5ns。

如圖所示為由OPA660與緩沖放大器BUF600構成的比較(低抖動)電路。比較器電路的基準電壓由電位器R2設定(R2也可用于失調調節),信號電壓VI經過150Ω電阻加到OPA660內部 1放大器輸入端5腳,由 1放大器6腳輸出到OTA的2腳。2腳與3腳兩個信號比較,當2腳電壓>3腳電壓時,OPA660輸出端8腳為高電平;反之,當2腳電壓<3腳電壓時,OPA660輸出端8腳為低電平。OPA660輸出端8腳信號再經過緩沖放大器BUF600輸出。傳輸延時時間為5nS;上升時間為1.5ns。

如圖所示為由OPA660與緩沖放大器BUF600構成的比較(低抖動)電路。比較器電路的基準電壓由電位器R2設定(R2也可用于失調調節),信號電壓VI經過150Ω電阻加到OPA660內部 1放大器輸入端5腳,由 1放大器6腳輸出到OTA的2腳。2腳與3腳兩個信號比較,當2腳電壓>3腳電壓時,OPA660輸出端8腳為高電平;反之,當2腳電壓<3腳電壓時,OPA660輸出端8腳為低電平。OPA660輸出端8腳信號再經過緩沖放大器BUF600輸出。傳輸延時時間為5nS;上升時間為1.5ns。

Copyright ? 2005-2024 華北計算機系統工程研究所版權所有 京ICP備10017138號-2