1 引言

CPLD(Complex programmable Logic Device,復雜可編程邏輯器件)和FPGA(Field programmable Gates Array,現場可編程門陣列)都是可編程邏輯器件,它們是在PAL、GAL等邏輯器件基礎上發展起來的。同以往的PAL、GAL相比,FPGA/CPLD的規模比較大,適合于時序、組合等邏輯電路的應用。它可以替代幾十甚至上百塊通用IC芯片。這種芯片具有可編程和實現方案容易改動等特點。由于芯片內部硬件連接關系的描述可以存放在磁盤、ROM、PROM、或EPROM中,因而在可編程門陣列芯片及外圍電路保持不動的情況下,換一塊EPROM芯片,就能實現一種新的功能。它具有設計開發周期短、設計制造成本低、開發工具先進、標準產品無需測試、質量穩定以及實時在檢驗等優點,因此,可廣泛應用于產品的原理設計和產品生產之中。幾乎所有應用門陣列、PLD和中小規模通用數字集成電路的場合均可應用FPGA和CPLD器件。

在現代電子系統中,數字系統所占的比例越來越大。系統發展的越勢是數字化和集成化,而CPLD/FPGA作為可編程ASIC(專用集成電路)器件,它將在數字邏輯系統中發揮越來越重要的作用。

在數字邏輯電路設計中,分頻器是一種基本電路。通常用來對某個給定頻率進行分頻,以得到所需的頻率。整數分頻器的實現非常簡單,可采用標準的計數器,也可以采用可編程邏輯器件設計實現。但在某些場合下,時鐘源與所需的頻率不成整數倍關系,此時可采用小數分頻器進行分頻。比如:分頻系數為2.5、3.5、7.5等半整數分頻器。筆者在模擬設計頻率計脈沖信號時,就用了半整數分頻器這樣的電路。由于時鐘源信號為50MHz,而電路中需要產生一個20MHz的時鐘信號,其分頻比為2.5,因此整數分頻將不能勝任。為了解決這一問題,筆者利用VIDL硬件描述語言和原理圖輸入方式,通過MAX+plus II開發軟件和ALTERA公司的FLEX系列EPF10K10LC84-4型FPGA方便地完成了半整數分頻器電路的設計。

2 小數分頻的基本原理

小數分頻的基本原理是采用脈沖吞吐計數器和鎖相環技術先設計兩個不同分頻比的整數分頻器,然后通過控制單位時間內兩種分頻比出現的不同次數來獲得所需要的小數分頻值。如設計一個分頻系數為10.1的分頻器時,可以將分頻器設計成9次10分頻,1次11分頻,這樣總的分頻值為:

F=(9×10+1×11)/(9+1)=10.1

從這種實現方法的特點可以看出,由于分頻器的分頻值不斷改變,因此分頻后得到的信號抖動較大。當分頻系數為N-0.5(N為整數)時,可控制扣除脈沖的時間,以使輸出成為一個穩定的脈沖頻率,而不是一次N分頻,一次N-1分頻。

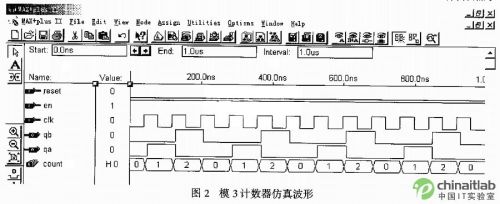

圖2 模3計數器仿真波形

3 電路組成

分頻系數為N-0.5的分頻器電路可由一個異或門、一個模N計數器和一個二分頻器組成。在實現時,模N計數器可設計成帶預置的計數器,這樣可以實現任意分頻系數為N-0.5的分頻器。圖1給出了通用半整數分頻器的電路組成。

采用VHDL硬件描述語言,可實現任意模N的計數器(其工作頻率可以達到160MHz以上),并可產生模N邏輯電路。之后,用原理圖輸入方式將模N邏輯電路、異或門和D觸發器連接起來,便可實現半整數(N-0.5)分頻器以及(2N-1)的分頻。

4 半整數分頻器設計

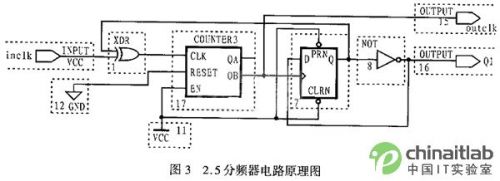

現通過設計一個分頻系數為2.5的分頻器給出用FPGA設計半整數分頻器的一般方法。該2.5分頻器由模3計數器、異或門和D觸發器組成。

圖3 2.5分頻器電路原理圖

4.1 模3計數器

該計數器可產生一個分頻系數為3的分頻器,并產生一個默認的邏輯符號COUNTER3。其輸入端口為RESET、EN和CLK;輸出端口為QA和QB。下面給出模3計數器VHDL描述代碼:

library ieee;

use ieee.std-logic-1164.all;

use ieee.std-logic-unsigned.all;

entity counter3 is

port(clk,reset,en:in std-logic;

qa,qb:out std-logic);

end counter3;

architecture behavior of counter3 is

signal count:std-logic-vector(1 downto 0);

begin

process(reset,clk)

begin

if reset='1'then

count(1 downto 0)<="00";

else

if(clk 'event and clk='1')then

if(en='1')then

if(count="10")then

count<="00";

else

count<=count+1;

end if;

end if;

end if;

end if;

end process;

qa<=count(0);

qb<=count(1);

end behavior;

任意模數的計數器與模3計數器的描述結構完全相同,所不同的僅僅是計數器的狀態數。上面的程序經編譯、時序模擬后,在MAX+PLUS II可得到如圖2所示的仿真波形。

4.2 完整的電路及波形仿真

將COUNTER3、異或門和D觸發器通過圖3所示的電路邏輯連接關系,并用原理圖輸入方式調入圖形編輯器,然后經邏輯綜合即可得到如圖4所示的仿真波形。由圖中outclk與inclk的波形可以看出,outclk會在inclk每隔2.5個周期處產生一個上升沿,從而實現分頻系數為2.5的分頻器。設inclk為50MHz,則outclk為20MHz。因此可見,該電路不僅可得到分頻系數為2.5的分頻器(outclk),而且還可得到分頻系數為5的分頻器(Q1)。

5 結束語

選用ALTERA公司FLEX系列EPF10K10LC84-4型FPGA器件實現半整數分頻后,經邏輯綜合后的適配分析結果如表1所列。本例中的計數器為2位寬的位矢量,即分頻系數為4以內的半整數值。若分頻系數大于4,則需增大count的位寬。

| 選用器件 | I/O延遲時間 | 使用引腳數 | 工作頻率 |

| EPF10K10LC844 | 17.7ns | 5/84(5.95%) |

68.02MHz |

表1 半整數分頻器適配分析結果