1 FIR濾波器的參數(shù)設(shè)計

1.1 設(shè)計要求

數(shù)字濾波器實際上是一個采用有限精度算法實現(xiàn)的線性非時變離散系統(tǒng),它的設(shè)計步驟為先根據(jù)需要確定其性能指標,設(shè)計一個系統(tǒng)函數(shù)H(z)逼近所需要的技術(shù)指標,最后采用有限精度算法實現(xiàn)。本系統(tǒng)的設(shè)計指標為:設(shè)計一個16階的低通FIR濾波器,對模擬信號的采樣頻率Fs為48KHz,要求信號的截止頻率Fc=10.8kHz,輸入序列為寬為9位(最寬位為符號位)。

1.2 FIR濾波器的參數(shù)選取 設(shè)計頻率選擇性數(shù)字濾波器時,通常希望能有近似恒定的頻響幅度,并盡量減小通帶內(nèi)的相位失真,斜率為整數(shù)的線性相位對應于時域中簡單的延時,他在頻域中可將相位失真降低到最小的程度[2],用Matlab提供的濾波器設(shè)計的專門工具箱--FDAtool仿真設(shè)計濾波器,滿足要求的FIR濾波器幅頻特性,如圖1所示。

2 數(shù)字濾波器的DSP Builder設(shè)計

2.1 DSP Builder介紹

DSP Builer是Altera推出的一個數(shù)字信號處理(DSP)開發(fā)工具,他在Quartus II FPGA設(shè)計環(huán)境中集成了Mathworks的Matlab和Simulink DSP開發(fā)軟件[3]。對DSP Builder而言,包括DSP系統(tǒng)的建模,系統(tǒng)級仿真、設(shè)計模型向VHDL硬件描述語言代碼的轉(zhuǎn)換、RTL(Register Transfer Level,邏輯綜合)級功能仿真測試、編譯適配和布局布線、時序?qū)崟r仿真直至對DSP目標器件的編程配置,整個開發(fā)流程幾乎可以在頂層的開發(fā)工具Matlab/Simulink同一環(huán)境中完成。

2.2 FIR 濾波器算法模型建立

根據(jù)FIR濾波器原理,可以利用FPGA來實現(xiàn)FIR濾波電路,DSP Builder設(shè)計流程的第一步是在Matlab/Simulink中進行設(shè)計輸入,即Matlab的Simulink環(huán)境中建立一個MDL模型文件,用圖形方式調(diào)用Altera DSP Builder和其他的Simulink庫中的圖形模塊,構(gòu)成系統(tǒng)級或算法級設(shè)計框圖(或稱Simulink建模)。

2.3 基于DSP Builder的系統(tǒng)級仿真

輸入信號采用頻率分別為f1=8KHz和f2=16KHz的兩個正弦信號進行疊加,其中的仿真波形如圖2所示,從FIR濾波電路的仿真結(jié)果看出,輸入信號通過濾波器后輸出基本上變成單頻率的正弦信號,至此完成了模型仿真。

3 基于 FPGA的數(shù)字濾波器的實現(xiàn)

3.1 運用Modelsim進行功能仿真

在DSP Builder中進行的仿真是屬于系統(tǒng)驗證性質(zhì)的,是對MDL文件進行的仿真,并沒有對生成的VHDL代碼進行過仿真。事實上,生成VHDL描述是RTL級的,是針對具體的硬件結(jié)構(gòu)的,這兩者之間有可能存在軟件理解上的差異,轉(zhuǎn)換后的VHDL代碼實現(xiàn)可能與MDL模型描述的情況不完全相符,這就需要針對生成的RTL級VHDL代碼進行功能仿真。

我們利用Modelsim來對生成的VHDL代碼進行功能仿真。設(shè)置輸入輸出信號均為模擬形式,出現(xiàn)如圖3所示的仿真波形,可以看到這與Simulink里的仿真結(jié)果基本一致。即可在Quartus II環(huán)境下的硬件設(shè)計[4]。

3.2 在FPGA器件中實現(xiàn)FIR濾波器

用FPGA實現(xiàn)的數(shù)字濾波器處理的是數(shù)字信號,在實際應用中,首先就要用A/D轉(zhuǎn)化器對模擬信號進行采樣與量化。傳統(tǒng)的方法多數(shù)是用CPU或單片機完成的,缺點是控制周期長,速度慢。而利用同步時序狀態(tài)機來控制A/D采樣是一種既簡單可靠,又能顯著提高采樣周期的行之有效的方法。

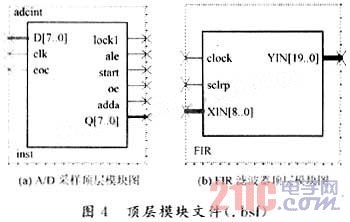

在Quartus II環(huán)境通過VHDL語言按要求設(shè)計該狀態(tài)機并轉(zhuǎn)換為.bsf文件;打開DSP Builder建立的Quartus II項目文件fir.qpf及fir.vhd并轉(zhuǎn)換為相應的.bsf文件,由此可以得到對應設(shè)計的模塊,如圖4所示,調(diào)用這兩個模塊建立新的頂層原理圖文件,在軟件環(huán)境里通過時序仿真,指定器件管腳、進行編譯、最后下載到實驗箱的EP1K10TC100-3器件中。

4 結(jié)語

用信號發(fā)生器產(chǎn)生所要求的兩個不同頻率的正弦信號,就可以示波器上看到濾波以后的結(jié)果,需要設(shè)計不同的濾波電路時,僅修改濾波器模型文件就可以實現(xiàn)。可見在利用FPGA進行數(shù)字濾波器的開發(fā)時,采用DSP Builder作為設(shè)計工具能快捷、可靠地設(shè)計實用濾波系統(tǒng)。