引言

數據進入FPGA的速率高于傳出的速率,持續的傳輸會造成數據的溢出,斷續的傳輸可能會造成數據不連續。使用基于LabVIEW FPGA的DMA FIFO作為主控計算機和FPGA之間的緩存,若DMAFIFO深度設置的合適,FIFO不會溢出和讀空,那么就能實現數據輸出FPGA是連續的。

本文在介紹了LabVIEW FPGA模塊程序設計特點的基礎上,結合DMA FIFO的工作原理,提出了一種設定FIFO深度的方法,解決了FIFO溢出、讀空的問題,實現了數據的連續傳輸。實驗結果表明該方法正確、可行,程序設計滿足系統對數據傳輸連續性的要求。

1 LabVIEW FPGA模塊

LabVIEW FPGA是LabVIEW的一個子模塊,使用該模塊可以通過圖形化的編程對NI公司RIO(Reconfigurable I/O)設備上的FPGA進行配置。圖形化的程序直接在硬件上實現,通過對RIO設備上的I/O接口的控制,可以靈活地對I/O信號進行分析和處理,表現出比固定I/O硬件更加優異的特性。使用LabVIEWFPGA模塊開發出來的系統具有開發周期短、結構模塊化、升級方便等優點。例如,圖1表示了一個用LabVIEW FPGA模塊設計的程序,在FPGA上實現方波發生器。該方波發生器通過數字接口DIO_1輸出方波,其占空比和周期可調。LabVIEW FPGA模塊在程序的設計與實現上都展現出了極大的靈活性。

1.1 LabVIEW FPGA程序開發流程

使用LabVIEW FPGA模塊開發應用程序的流程如圖2所示。首先創建FPGA vi,之后用FPGA設備仿真器在主控計算機上運行程序,反復地調試、修改,直至程序正確無誤。然后編譯FPGA vi,并把程序下載到FPGA上。FPGA部分的程序完成后,再根據需要在主控計算機上創建用戶界面程序Host vi,最終就完成整個系統的設計。

FPGA設備仿真器的打開方法是:首先在“項目瀏覽器”窗口中的打開“我的電腦”子菜單,右擊子菜單中的“FPGA Target”并在快捷菜單中選擇“Execute vion”下一級子菜單中的“Development Computer with Simulated I/O”。然后再在FPGA vi中點擊“Run”按鈕,這時程序在FPGA的設備仿真器上運行。

1.2 開發FPGA vi

發應用程序的第一步是創建用于配置PXIe-5641R板載FPGA的程序。在FPGA vi中可以實現算法邏輯,包括信號同步,定制數字通信協議,板載控制和預警處理判決機制等功能。通過LabVIEW FPGA模塊,可使用LabVIEW開發環境和許多類似的功能。但是由于FPGA不支持浮點操作,所以LabVIEW FPGA模塊較之LabVIEW完整Windows版開發軟件缺少了一些操作符和分析函數。另外,由于PXIe-5641R板卡沒有硬盤和操作系統,因此不支持文件I/O和ActiveX功能。LabVIEW FPGA模塊的函數面板如圖3所示。

硬件對象不管是FPGA設備還是FPGA仿真器,都可以訪問LabVIEW FPGA函數。仿真器使用RIO設備的I/O接口,可在主機處理器上執行邏輯算法。檢驗vi設計中的一些簡單性錯誤,避免不必要的反復編譯,尤其是在程序比較大的時候可節省大量的時間,提高編程效率。也可使用仿真器驗證vi的執行流程,但無法驗證硬件的確定性,若需要驗證硬件性能的確定性,必須對FPGA vi進行編譯。與其他FPGA開發工具一樣,根據應用程序的復雜程度和計算機資源的不同,編譯步驟可能要花上幾分鐘到幾個小時的時間。

1.3 開發Host vi

在FPGA vi完成調試、編譯、下載到板卡之后,就需要在主控計算機上創建一個用戶界面程序Host vi。在用戶界面應用程序中可以完成一些實時性要求不高的操作,例如配置系統參數,管理數據等。Host vi通過FPGA接口函數與FPGA vi進行通信,以及處理中斷。FPGA接口函數面板會在安裝LabVIEW FPGA模塊之后,自動添加到LabVIEW的函數面板中。LabVIEW函數面板中的FPGA接口函數面板如圖4所示。

2 不同時鐘域的數據連續傳輸

本文中的中頻信號生成系統是將主控計算機模擬生成的數據通過FPGA送到AD9857發送出去。數據進入FPGA的速率為52 MB/s,由于計算機的非實時性呈現斷續的形式,其實際的速率要低一些;數據傳出FPGA時,其數據位寬為16 b,輸出頻率為10 MHz,固其持續傳輸速率為20 MB/s。數據進入FPGA的速率高于出FPGA的速率,這就造成數據在不同時鐘域之間傳輸的問題。為了避免數據的溢出和保證數據連續性,本文使用DMA FIFO作為主控計算機與FPGA之間的緩存。它的存儲空間包括兩部分:一是主控計算機部分,主控計算機開辟一塊內存作為FIFO緩存;二是FPGA部分,FIFO占用部分Block Memory資源作為緩存。二者共同組成一個完整的FIFO,通過PXIe總線傳遞數據。FIFO的傳輸機制是:主控計算機首先把一個數組的數據存入作為FIFO緩存的內存中;DMA控制器會自動查詢FPGA上的FIFO剩余空間,當滿足緩存剩余空間大于數據塊容量的條件時,控制器通過PXIe總線把整個數據塊一并送入FPGA上的FIFO中;FPGA FIFO再將數據順序送出。

若在主控計算機向FIFO兩次寫入數據的間隔期間,FIFO中的數據保持不被讀空,就能保證輸出FPGA的數據是連續的。而合適的FIFO深度是FIFO不被讀空的基礎,所以確定FIFO深度的設定方法是數據在不同時鐘域之間實現連續傳輸的關鍵。

3 FIFO深度的設定方法

3.1 FPGA FIFO深度的設定

DMA控制器將數據從主控計算機內存整塊的傳送到FPGA的FIFO緩存中,所以FIFO的深度要大于數據塊的大小。LabVIEW FPGA里塊存儲FIFO是以2 KB大小來應用的。DMA FIFO使用RIO設備可獲取的內置RAM來存儲數據信息,該存儲空間與內存讀/寫是共享的。所以要留一部分RAM空間進行內存的讀/寫,FIFO的最大值為RAM容量減去16 KB。PXIe-5641R的RAM的容量是1 098 KB,所以,FPGAFIFO的深度設定范圍為2~1 082 KB。

另一方面,實際上LabVIEW為了能使FPGA高效運行,對Block Memory方式FIFO的大小作了規定,其大小只能為2M-1(數據由FPGA傳向主控計算機)或2M+5(數據由主控計算機傳向FPGA),M為數據的地址寬度;當設定值不是這些標準值時,LabVIEW會自動的放大到距其最近的一個標準值。這樣就確定了FPGAFIFO的深度,但是還不能保證數據能夠連續輸出。

3.2 主控計算機FIFO深度的設定

由于對主控計算機內存部分FIFO的讀/寫是以數組形式斷續進行的。所以,數組的長度和兩次寫入的間隔時間是能否保證數據連續性的重要參數,同時考慮到數據輸出FPGA是連續且頻率固定的。根據FIFO不讀空的原則推測:當寫入內存的數組的長度N與數據寫入內存的時間T和數據輸出FPGA的頻率F之間滿足如下的關系時,就能做到數據的連續傳輸:

N/T>F (1)

鑒于主控計算機操作系統的非實時性,需要將主控計算機FIFO深度D的大小設定為N的若干倍;通過大量實驗并與NI工程師討論,確定當FIFO的深度D的大小為N的3~5倍時,可完全滿足數據連續傳輸的要求。

3.3 實驗驗證

數據寫入內存的時間與主控計算機運行速度以及數組的大小有關。表1所示的是數組長度和寫入內存的時間與輸出數據連續性之間關系的實驗結果。其中,平均寫入內存時間指的是同一個數組循環執行寫入操作10萬次得到的平均結果。輸出FPGA的速率為10 MHz。

當數組長度較小時,單位時間內寫入到內存中的數據較少,內存里的數據不能滿足FPGA FIFO讀取數據的需求,在下一組數據到達之前內存里的數據已經讀空,故輸出的數據不能連續。當數組長度增大之后,單位時間寫入到內存的數據量也隨之增大,內存里的數據能夠滿足FP-GA FIFO讀取數據的需求,在內存讀空之前把下一組數據送入了內存,所以輸出的數據能夠保持連續性。實驗結果驗證了上述推測公式的正確性。

4 數據連續傳輸的LabVIEW實現

在本文中系統軟件包括兩部分:Host vi和FPGAvi,二者是獨立而又有聯系的兩個部分。Host vi運行于主控計算機上,FPGA vi運行于FPGA上,二者通過FIFO來傳輸數據。

4.1 FPGA程序設計

使用圖形化的編程環境LabVIEW FPGA模塊來定義FPGA邏輯,除了具有上述的優點以外,LabVIEW作為一種并行結構的編程語言,非常適用于FPGA的并行結構,能夠十分方便地實現多線程并行任務。

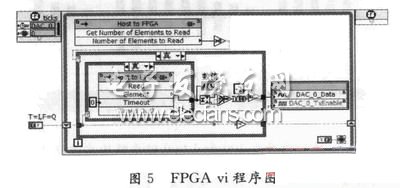

當FPGA vi開始運行時,從Host vi讀取數據的FIFO需要一定的初始化時間,時間長度與FIFO的深度成正比。在初始化期間FIFO輸出一系列的無效默認值。為了不讓無效值進入到下一級的運算中,在DMA方式的FIFO之前加了一個FIFO函數——Get Number of Element to Read,該函數用于獲得FIFO內有效數據的數量。當有效數據的數量大于0時,再開始進行下一級運算。考慮到FPGA有限的硬件資源和FPGA FIFO最小值的限制,將數據的地址寬度設為M=11,根據上文分析DMA FIFO的深度設為2M+5=2 053 KB。

4.2 主控計算機程序設計

Host vi是系統程序的另一部分部分,它具有建立硬件對象(FPGA)、與硬件通信和圖形顯示等功能。主控計算機程序圖如圖6所示,首先要建立與之進行通信的硬件對象,即FPGA;其次配置系統時鐘、輸出模式;再次創建FIFO,設置其在主控計算機部分的FIFO深度;然后從電子表格讀取數據,并循環查詢FIFO剩余空間的大小,當剩余空間大于數組長度時,數據寫入FIFO當沒有足夠的空間時,數據保留到下一個循環,滿足條件后再寫入FIFO;最后關閉FIFO應用,處理錯誤。

當輸入數組長度分別為300和1 000,形狀如圖7所示的波形時,輸出數據的波形如圖8所示。由于AD9857上變頻的原因,使得輸出波形在輸入的矩形包絡中帶有載波,載波頻率為60 MHz。根據表1中的數據可以得出結論:此處的編程和上述實驗的結果是一致的,即FPGA輸出頻率為10 MHz,數組長度大于500時,系統數據的輸出是連續。同時此結果也表明本文中的LabVIEW程序實現了數據的連續傳輸。

5 結語

通過設定合適的FIFO深度,實現了數據的連續傳輸,為后續的工程設計奠定了基礎。該設定FIFO深度的方法也對其他使用LabVIEW FPGA模塊的工程設計具有一定的參考價值。