1 引言

電荷耦合器CCD具有尺寸小、精度高、功耗低、壽命長、測量精度高等優點,在圖像傳感和非接觸測量領域得到了廣泛應用。由于CCD芯片的轉換效率、信噪比等光電特性只有在合適的時序驅動下才能達到器件工藝設計所要求的最佳值,以及穩定的輸出信號,因此驅動時序的設計是應用的關鍵問題之一。通用CCD驅動設計有4種實現方式:EPROM驅動法;IC驅動法;單片機驅動法以及可編程邏輯器件(PLD)驅動法。

基于FPGA設計的驅動電路是可再編程的,與傳統的方法相比,其優點是集成度高、速度快、可靠性好。若要改變驅動電路的時序,增減某些功能,僅需要對器件重新編程即可,在不改變任何硬件的情況下,即可實現驅動電路的更新換代。

2 CD 1501D CCD工作參數及時序分析

2.1 TCDl50lD CCD工作參數

所選器件是日本TOSHIBA公司的TCDl50lD CCD作為光電傳感器,該芯片是高靈敏度、低噪聲和寬動態范圍的線陣CCD器件。主要參數如下:

光敏像元數:5000個 像元尺寸:7μm×7μm×7μm

光譜響應范圍:300~l 000 nm靈敏度:10.4~15.6V/Lx.s

動態范同典型值:3 000 nm飽和曝光度典型值:0.23Lx.s

驅動時鐘頻率最大值:12 MHz

該器件正常工作的驅動脈沖主要有:復位時鐘RS、移位脈沖φ1、φ2和轉移脈沖SH。該器件具有5 000個有效像元,正常工作還需要76個虛設單元輸出(dummy outputs)信號。由于該器件是兩列并行傳輸,所以在一個周期內至少需要2538個φ1(或φ2)時鐘脈沖才能完成一幀圖像轉移。

2.2 驅動時序分析

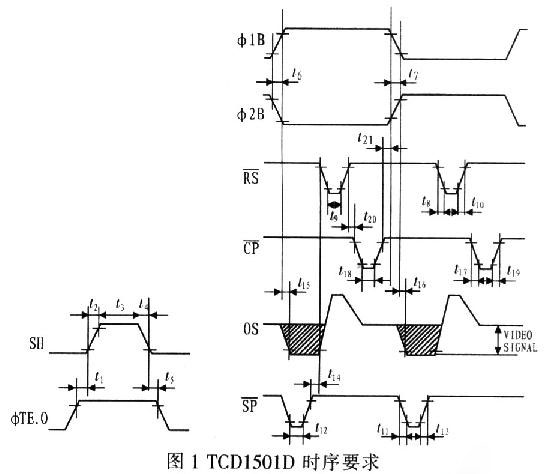

各驅動時序之間正確的先后關系是保證CCD正常工作的前提。具體時序關系如圖1所示。

3 CCD輸出信號的采集

CCD器件輸出的原始信號中除了有用的信號外,還夾雜著各種噪聲和干擾,主要有光子噪聲、散粒噪聲、暗電流噪聲、復位噪聲以及輸出噪聲等,而影響最大的是復位噪聲。通過理論及實驗可知,相關雙采樣是消除復位噪聲最有效的方法之一。其原理是利用復位噪聲在同一像素周期內近似為常數,因此,只要把同一像素周期內的參考電平和信號電平進行兩次采樣,再進行相減,即可消除復位噪聲。

3.1 內部信號處理

與其他線陣CCD不同的是TCDl50lD內部包含有采樣保持電路。由圖1可知,OS經SH脈沖采樣后,得到所有視頻信號的包絡,經CP箝位電平后輸出一個大概為5 V左右的直流分量,兩個波形再通過差分即可得到有用的視頻信號。若要保證信號的不失真輸出,則t12和t18需越小越好,必須滿足時間最小值要求,即讓采樣脈沖SH和箝位脈沖CP對OS信號在很短時間內準確地對陰影部分信號電平和參考電平分別進行采樣,然后兩者差分。輸出視頻信號的示意圖如圖2所示,圖2(a)中的陰影部分是有用的視頻信號,白色部分是參考電平,圖2(b)是相關雙采樣后CCD每個像元中視頻信號包絡的集合,是一個負極性的離散模擬信號,圖2(c)是翻轉之后的正極性信號。這個過程相當于對CCD輸出信號進行內部CDS,由于CCD內部時序要求非常嚴格,在某些情況下可以采用外部的相關雙采樣技術,在實際應用中可根據具體情況選擇使用內部采樣處理還是外部采樣處理。

3.2 外部信號采集

外部電路對CCD信號采集主要包括除噪和A/D轉換,前者是為了在不損失圖像細節的前提下盡可能消除噪聲和干擾,以獲取高質量的圖像;后者則是為了完成對輸出信號的數字化,以便進一步進行軟件處理。

傳統CCD除噪和A/D轉換是采用分立電路來完成對輸出信號的數字化處理,對于高速采集系統而言,傳統方法顯然滿足不了要求。為了簡化電路設計、提高系統可靠性,這里采用單片集成的CCD模擬信號的預處理芯片AD9826來完成CDS及A/D轉換。該芯片內部集成了CDS電路和16位20MHz A/D轉換器。而AD9826輸出只有8位,因此采用分時輸出高8位和低8位的方法來實現16位數據的輸出.方框圖如圖3所示。由于AD9826對輸入信號幅值的要求可以達到4V,而未經處理的TCDl501D輸出信號幅值為3 V左右,其中還有一個接近5 V的直流分量,需用一個差分放大器消除直流后,再放大才能接到AD9826的輸入端,實現對CCD輸出信號不失真的進行處理。AD9826的CDSCLK時序驅動脈沖由FPGA產生,串口的配置可通過單片機或DSP寫入。

4 時序設計及波形仿真

通過對TCDl50lD的驅動脈沖及時序關系的分析,下面將用ALTERA公司的Quartus II 7.2作為開發平臺,對各路時序進行相關的設計及仿真。Quartus II 7.2開發系統是一種全集成化的可編程邏輯設計環境,它支持硬件描述語言(VHDL)、狀態圖及原理圖3種輸入方式,設計包括4個階段:設計輸入;設計實現;設計驗證和器件編程。其原理輸入方式簡單直觀,而硬件描述語言輸入方式的優點是可移植性和可讀性好,因而系統采用VHDL語言的輸入方式。

4.1 TCDl501D時序設計及仿真

系統所選的基準時鐘為100 MHz,工作頻率為10 MHz。依據TCDl501D驅動時序要求,采用硬件編程語言(VHDL)的輸入方式,設計出各脈沖產生的程序。各項驅動脈沖均由基準時鐘分頻產生。其脈沖參數分別為:φl=φ2=5 MHz,占空比為1:1,波形為方波,φ1、φ2在并行轉移時有一個大于SH高電平的寬脈沖,脈寬為2000 ns;復位脈沖RS=10MHz:占空比為3:2,波形為方波;SH在轉移時的寬脈沖為1000 ns;箝位脈沖CP和采樣保持脈沖SP分別為RS脈沖的延遲。正確編譯后,最后通過波形仿真,得到TCDl501D驅動時序的仿真波形圖,仿真結果如圖4所示,其中FlB、F2B分別表示移位脈沖φ1、φ2,圖中+2.011885 μs線表示相對于25.446 ns的基準線偏移量,可知F1B寬脈沖幾乎為2 000 ns,能滿足器件手冊的要求。同理,可判定其他驅動脈沖也滿足要求。

4.2 AD9826時序設計及仿真

通過對AD9826單通道CDS采樣時序分析,結合TCDl501D輸出信號的特點,設計出正確合理的CDS驅動時序是保證該器件正常工作的基礎。充分利用硬件編程語言(VHDL)的優點,產生各項時序。依據TCDl501D輸出信號OS的時序要求及AD9826對CDS的要求,可設定各脈沖的參數為:主時鐘為100 MHz,CDSCLK1=CDSCLK2=10 MHz,占空比為l:4,兩次采樣間隔為40 ns,均為下降沿采樣;AD—CCLK=10MHz,占空比為1:l,低電平有效。編譯后通過波形仿真的結果如圖5所示,其中12.211 ns線為基準,+100.62ns線為相對基準線的偏移量,可知CDSCLKl周期為100 ns,滿足器件手冊中所規定的要求。

5 結語

通過對TCDl50lD輸出圖像信號特征的簡要分析,分別闡述了內、外2種除噪方法,并給出了相應的時序,再利用Quartus II 7.2軟件平臺對TCDl501D CCD驅動時序及AD9826的采樣時序進行了設計及結果仿真,使CCD的驅動變得簡單且易于處理,這是傳統邏輯電路無法比擬的,對其他CCD時序驅動及后續處理提供了一定的參考價值。