摘 要: 介紹EDA技術在一個簡單的數字系統設計中的具體應用過程,詳細闡述了EDA技術的基本特征和發展趨勢,揭示了其在現代數字系統中的重要地位及作用。

關鍵詞: EDA ASIC PLD FPLD VHDL 數字系統 自頂向下 并行工程 ISP

二十世紀后半期,隨著集成電路和計算機技術的飛速發展,數字系統也得到了飛速發展,其實現方法經歷了由分立元件、SSI、MSI到LSI、VLSI以及UVLSI的過程。同時,為了提高系統的可靠性與通用性,微處理器和專用集成電路(ASIC)逐漸取代了通用全硬件LSI電路,而在這二者中,ASIC以其體積小、重量輕、功耗低、速度快、成本低、保密性好而脫穎而出。總的來說,ASIC的制作可粗略地分為掩膜方法和現場可編程方法兩大類。目前,業界大量可編程邏輯器件(PLD),尤其是現場可編程邏輯器件(FPLD)被大量地應用在ASIC的制作當中。在可編程集成電路的開發過程中,電子設計自動化(EDA)技術應運而生。EDA技術的出現,不僅為電子系統設計帶來了一場革命性的變化,從某種角度來說,也成為其發展的必然。

1 EDA技術的基本特征及發展

1.1 EDA技術的基本概念

EDA(Electronics Design Automation)即電子設計自動化技術,是一種以計算機為基本工作平臺,利用計算機圖形學、拓撲邏輯學、計算數學以至人工智能學等多種計算機應用學科的最新成果而開發出來的一整套軟件工具,是一種幫助電子設計工程師從事電子元件產品和系統設計的綜合技術。

1.2 EDA技術的發展歷程及發展趨勢

EDA技術的發展經歷了一個由淺到深的過程。二十世紀70年代,隨著中小規模集成電路的開發應用,傳統的手工制圖設計印刷電路板和集成電路的方法已無法滿足設計精度和效率的要求,因此工程師們開始進行二維平面圖形的計算機輔助設計,以便解脫繁雜、機械的版圖設計工作,這就產生了第一代EDA工具。

到了80年代,為了適應電子產品在規模和制作上的需要,應運出現了以計算機仿真和自動布線為核心技術的第二代EDA技術。其特點是以軟件工具為核心,通過這些軟件完成產品開發的設計、分析、生產、測試等各項工作。

90年代后,EDA技術繼續發展,出現了以高級語言描述、系統級仿真和綜合技術為特征的第三代EDA技術。它們的出現,極大地提高了系統設計的效率,使廣大的電子設計師開始實現“概念驅動工程”的夢想。設計師們擺脫了大量的輔助設計工作,而把精力集中于創造性的方案與概念構思上,從而極大地提高了設計效率,縮短了產品的研制周期。

由此可見,EDA技術可以看作是電子CAD的高級階段。EDA工具的出現,給電子系統設計帶來了革命性的變化。隨著Intel公司Pentium處理器的推出,Xilinx等公司幾十萬門規模的FPGA的上市,以及大規模的芯片組和高速、高密度印刷電路板的應用,EDA技術在仿真、時序分析、集成電路自動測試、高速印刷電路板設計及操作平臺的擴展等方面都面臨著新的巨大的挑戰。這些問題實際上也是新一代EDA技術未來發展的趨勢。

1.3 EDA技術的基本特征和基本工具

總的來說,現代EDA技術的基本特征是采用高級語言描述,具有系統級仿真和綜合能力。它主要采用并行工程和“自頂向下”的設計方法,使開發者從一開始就要考慮到產品生成周期的諸多方面,包括質量、成本、開發時間及用戶的需求等等。然后從系統設計入手,在頂層進行功能方框圖的劃分和結構設計,在方框圖一級進行仿真、糾錯,并用VHDL、Verilog-HDL、ABEL等硬件描述語言對高層次的系統行為進行描述,在系統一級進行驗證,最后再用邏輯綜合優化工具生成具體的門級邏輯電路的網表,其對應的物理實現級可以是印刷電路板或專用集成電路。近幾年來,硬件描述語言等設計數據格式的逐步標準化、不同設計風格和應用的要求導致各具特色的EDA工具被集成在同一個工作站上,從而使EDA框架日趨標準化。

EDA工具的發展經歷了兩個大的階段:物理工具和邏輯工具。現在EDA和系統設計工具正逐漸被理解成一個整體的概念:電子系統設計自動化。物理工具用來完成設計中的實際物理問題,如芯片布局、印刷電路板布線等等;邏輯工具是基于網表、布爾邏輯、傳輸時序等概念,首先由原理圖編輯器或硬件描述語言進行設計輸入,然后利用EDA系統完成綜合、仿真、優化等過程,最后生成物理工具可以接受的網表或VHDL、Verilog-HDL的結構化描述。現在常見的EDA工具有編輯器、仿真器、檢查/分析工具、優化/綜合工具等等。

目前,PLD已成為現代數字系統設計的主要手段。傳統的編程技術是將PLD器件插在編程器上進行編程,而“在系統可編程”(ISP,即In-System Programmable)邏輯器件的問世,將可編程器件的優越性發揮到了極致。它允許用戶“在系統中”編輯和修改邏輯,給使用者提供了在不修改系統硬件設計的條件下重構系統的能力和硬件升級能力,使硬件修改變得象軟件修改一樣方便,系統的可靠性因此而提高。ISP技術即直接在用戶設計的目標系統中或線路板上對PLD器件進行編程的技術,打破了使用PLD必先編程后裝配的慣例,而可以先裝配后編程,成為產品后還可反復編程,從而開創了數字電子系統設計技術新的一頁。

下面,筆者即以基于Xilinx的CPLD器件XC95108-7PC84C和Foundation 2.1軟件平臺的一個簡單的四位扭環形計數器(即四位循環彩燈)的設計為例,談談EDA技術在ISP數字邏輯系統中的具體應用。

2 EDA技術在一個簡單的數字系統設計中的具體應用

2.1 設計要求

本系統要求設計一個四位扭環形計數器,時鐘上升沿觸發,可進行復位(即清零)和時鐘使能控制,其結果要求通過四個一字排列的發光二極管顯示出來(構成一種簡單的循環彩燈圖案),同時其輸出讀數(十六進制)亦要求通過數碼管進行顯示。

2.2 設計分析

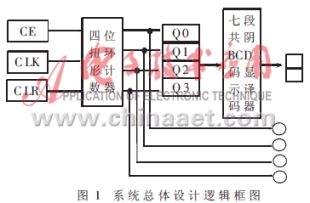

根據設計要求,本系統可以通過四個帶時鐘使能和異步清零端的上升沿觸發的D觸發器來完成計數部分,且時鐘同步,若四位輸出的初始值為“0000”,則經過8個時鐘脈沖激勵的輸出依次為:“0001”(1)、“0011”(3)、“0111”(7)、“1111”(F)、“1110”(E)、“1100”(C)、“1000”(8)、“0000”(0)。這些時刻的輸出,一方面將送至發光二極管進行顯示;另一方面將送至數碼管的七個管腿,并通過七段共陰BCD碼顯示譯碼器顯示該讀數。總的邏輯框圖如圖1所示。

2.3 具體實現

經過總體分析即“頂層”設計之后,就可以利用EDA工具和ISP技術“向下”進行具體的模塊設計了。

2.3.1 邏輯輸入

2.3.1.1 計數器部分

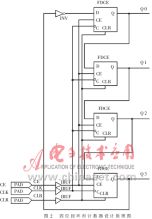

EDA工具的重要特征之一是支持多種輸入方式,如原理圖輸入方式、狀態機輸入方式、HDL高級語言輸入方式等等。Foundation 2.1軟件平臺對以上三種輸入方式都能很好地支持。此部分的設計即以原理圖輸入方式為例來實現。四位扭環形計數器原理圖如圖2所示。

2.3.1.2 數碼管顯示部分

實質上是設計一個4~7線的BCD碼顯示譯碼器。此部分擬用IEEE通用硬件描述語言VHDL來設計,完成編譯和綜合后即生成相應的宏模塊,設計代碼如下:

library IEEE;

use IEEE.std_logic_1164.all;

entity HEX2LED is

port (

HEX: in STD_LOGIC_VECTOR (3 downto 0);

LED: out STD_LOGIC_VECTOR (6 downto 0)

);

end HEX2LED;

architecture HEX2LED_arch of HEX2LED is

begin

with HEX SELect

LED<=“1111001” when “0001”, --1

“0100100” when “0010”, --2

“0110000” when “0011”,--3

“0011001” when “0100”,--4

“0010010” when “0101”,--5

“0000010” when “0110”,--6

“1111000” when “0111”,--7

“0000000” when “1000”,--8

“0010000” when “1001”,--9

“0001000” when “1010”,--A

“0000011” when “1011”,--b

“1000110” when “1100”,--C

“0100001” when “1101”,--d

“0000110” when “1110”,--E

“0001110” when “1111”,--F

“1000000” when others;--0

end HEX2LED_arch;

2.3.1.3發光二極管顯示部分

發光管的顯示只需將Q0~Q3的輸出引線直接與四個并行排列的發光二極管管腳一一相連即可。

至此,各部分設計工作基本完成,我們只需將各個部分按連線規則嚴格進行連接,定義好相應的I/O管腳和信號線后,即可進行邏輯實現與綜合了。

2.3.2 邏輯實現與綜合

EDA提供了良好的邏輯綜合與優化功能,它能夠將設計人員設計的邏輯級電路圖自動地轉換為門級電路,并生成相應的網表文件、時序分析文件和各種報表,若設計沒有錯誤,最終可生成可以編程下載的JED文件。

2.3.3 系統仿真

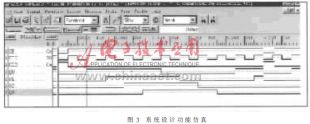

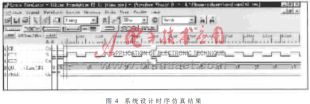

通常,在正式下載前,設計人員還要對設計的電路進行一些校驗工作,這些工作即可通過EDA的功能仿真和時序仿真工具來完成。本系統在設定了CLK、CE和CLR信號的情況下,輸出QO~Q3的功能仿真圖和時序仿真圖分別如圖3和圖4所示。由圖4可以看出,此設計的各信號的延遲在2ns左右,基本符合設計指標要求。

2.3.4 編程下載

當設計人員確定設計工作已基本成功時,即可通過編程電纜下載數據流來進行硬件驗證。驗證合格后,總體設計工作即圓滿完成。

通過此例的設計流程講述可知,EDA技術及其工具在數字電路系統(包括模擬電路系統)中正發揮著越來越重要的作用,其應用的深度和廣度正在向更深層次延伸。

目前,現代集成電路技術的發展使以現場可編程門陣列為代表的大容量可編程邏輯器件的等效門數迅速提高,其規模直逼標準門陣列,達到了系統集成的水平。特別是進入二十世紀90年代后,隨著CPLD、FPGA等現場可編程邏輯器件的逐漸興起,VHDL、Verilog等通用性好、移植性強的硬件描述語言的普及,ASIC技術的不斷完善,EDA技術在現代數字系統和微電子技術應用中起著越來越重要的作用。從通常意義上來說,現代電子系統的設計已經再也離不開EDA技術的幫助了。

參考文獻

1 黃正瑾.在系統編程技術及其應用.南京:東南大學出版社,1999.5

2 常 青.可編程專用集成電路的設計.北京:國防工業出版社,1998.1

3 賈新章,郝 躍.微電子學導論.北京:國防工業出版社,1995.7

4 Kevin Skahill.可編程邏輯系統的VHDL設計技術.東南大學出版社,1998.9