引言

在一些電磁環境比較惡劣的情況下,一些大規模集成電路常常會受到干擾,導致不能正常工作。特別是像RAM這種利用雙穩態進行存儲的器件,往往會在強干擾下發生翻轉,使原來存儲的"0"變為"1",或者"1"變為"0",造成的后果往往是很嚴重的。例如導致一些控制程序跑飛,存儲的關鍵數據出錯等等。現在,隨著芯片集成度的增加,發生錯誤的可能性也在增大。在一些特定的應用中,這已經成為一個不能忽視的問題。例如在空間電子應用領域,單粒子翻轉效應就成為困擾設計師的一個難題。

在這種情況下,我們可以采用錯誤檢測與糾正EDAC(ErrorDetectionAndCorrection)電路來有效地減少或避免這種情況的出現。根據檢錯、糾錯的原理,主要思想是在數據寫入時,根據寫入的數據生成一定位數的校驗碼,與相應的數據一起保存起來;當讀出時,同時也將校驗碼讀出,進行判決。如果出現一位錯誤則自動糾正,將正確的數據送出,并同時將改正以后的數據回寫覆蓋原來錯誤的數據;如果出現兩位錯誤則產生中斷報告,通知CPU進行異常處理。所有這一切動作都是靠硬件設計自動完成的,具有實時性和自動完成的特點。通過這樣的EDAC電路,能大大提高系統的抗干擾能力,從而提高系統的可靠性。

當然,有一些現成的集成電路芯片可以完成上述功能,如74系列的74630芯片等。但由于嵌入式系統中,往往由于集成化的需要,要將這樣的功能集成到FPGA中去實現,因此采用VHDL語言進行設計具有靈活性和通用性的特點。

1檢錯與糾錯原理

首先來看看檢錯和糾錯的基本原理。進行差錯控制的基本思想是在信息碼組中以一定規則加入不同方式的冗余碼,以便在信息讀出的時候依靠多余的監督碼或校驗碼來發現或自動糾正錯誤。

針對誤碼發生的特點,即錯誤發生的隨機性和小概率性,它幾乎總是隨機地影響某個字節中的某一位(bit),因此,如果能夠設計自動糾正一位錯誤,而檢測兩位錯誤的編碼方式,就可以大大的提高系統的可靠性。

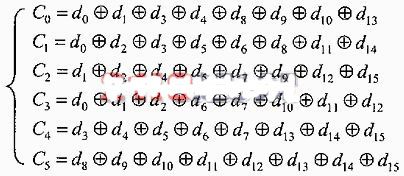

現在我們以16位的CPU數據總線為例,假定信息源的位數為16,要構造一種能夠糾正一位錯誤,檢查兩位錯誤的編碼方式。根據"糾錯定理",需要設計最小漢明距離≥4的碼組。我們可以采用線形分組碼,利用線性分組碼的概念可以構造六位監督碼,它們由如下線性關系產生:

其中,d0~d15為16位數據(15為最高位MSB,0為最低位LSB),C0~C5為產生的六位監督碼,表示進行異或運算。

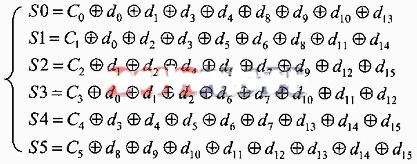

在數據讀出時,我們只需要考察伴隨式S=[S0S1S2S3S4S5],其中:

很容易證明,根據伴隨式進行誤差診斷,符合表1所列情況。

表1誤差診斷碼表

|

伴隨式 |

錯誤位置

|

||||||||||||||||||||||

|

數據位 |

校驗位 |

無錯 |

|||||||||||||||||||||

|

d0 |

d1 |

d2 |

d3 |

d4 |

d5 |

d6 |

d7 |

d8 |

d9 |

d10 |

d11 |

d12 |

d13 |

d14 |

d15 |

C0 |

C1 |

C2 |

C3 |

C4 |

C5 |

||

|

S0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

S1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

S2 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

S3 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

S4 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

S5 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

當S=[000000]時,數據正確無誤;

當S=[001011]時,數據錯一位,并且錯誤發生在d0位,可將d0位的數據取反加以糾正;

當S=[001101]時,數據錯一位,并且錯誤發生在d1位,可將d1位的數據取反加以糾正;

.

.

.

當S=[110100]時,數據錯一位,并且錯誤發生在d15位,可將d15位的數據取反加以糾正;

當S=[000001]時,數據錯一位,并且錯誤發生在C0位;

.

.

.

當S=[100000]時,數據錯一位,并且錯誤發生在C5位;

當S為其它情況時,至少發生兩位錯誤。

可以看出,這種編碼方式可以滿足自動糾正一位錯誤,而發現兩位錯誤的要求。下面就進一步討論如何用電路來實現。

2EDAC電路的設計

EDAC電路必須配合CPU的讀寫時序進行工作,不同類型CPU的時序往往是不一樣的。一般來說,總可以分為讀周期和寫周期。在寫周期時,按照上面的設計邏輯,根據16位數據位生成6位的校驗字,這時,數據位是輸入,校驗位是輸出,并在該寫周期中將數據位和校驗位都存儲到相應的存儲器位置中去,這種情況比較簡單。在讀周期時,情況復雜些,可以設計成三步完成。第一步,在CPU讀信號來之前,由于存儲器地址和片選信號已經有效,可先將數據位和校驗位讀入,這時,數據位和校驗位都是作為輸入。第二步,在讀信號來時,將數據位、校驗位鎖存,同時進行檢測,如果無錯,則不進行任何處理,直接將數據輸出;如果發現二位錯,則產生中斷;如果是一位錯,在輸出上有所反應,并進入下一步。第三步,如果是數據位出錯,將其自動更正,并將正確的值再回寫到相應的內存地址中,將正確的數據值輸出到數據總線;如果是校驗位出錯,可以直接將正確的數據位輸出到數據總線上。這部分功能是EDAC功能的核心,可以用VHDL語言來實現,以下是設計思路。

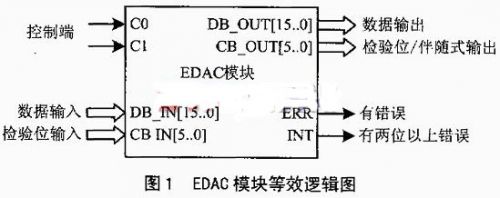

(1)對輸入的設計

①數據位和校驗位的輸入。

②控制端的輸入。經過前面的分析,一共有四種狀態(寫一種狀態、讀三種狀態),可以設計兩個控制端,設為C0、C1。其功能見表2。

(2)對輸出的設計

①數據位和校驗位的輸出。其中校驗位的輸出在讀周期和寫周期有所不同:在寫周期校驗位輸出是生成的校驗位;而讀周期就沒有必要輸出校驗位了,可以設計為輸出伴隨式S。

②錯誤標記輸出。在應用中,可以設計兩種錯誤標記輸出,分別記為ERR和INT。其中ERR輸出"1"表示數據位有錯誤產生,包括可自動糾正的一位錯誤和兩位或兩位以上錯誤。INT輸出"1"則表示發生了兩位或以上錯誤,無法自動糾正,向CPU申請中斷,由CPU進行異常處理。

在表2中,總結了上面所描述的功能設計。

表2EDAC模塊功能表

|

控制端 |

存儲器周期 |

功能描述 |

數據位 |

校驗位 |

錯誤標記輸出 |

||

|

C0 |

C1 |

ERR |

INT |

||||

|

0 |

0 |

寫周期 |

產生校驗位,并輸出 |

輸入 |

輸出 |

0 |

0 |

|

0 |

1 |

讀周期 |

讀入數據位和校驗位 |

輸入 |

輸入 |

0 |

0 |

|

1 |

1 |

讀周期 |

鎖存數據位和校驗位并進行錯誤檢測 |

鎖存 |

鎖存 |

0/1 |

0/1 |

|

1 |

0 |

讀周期 |

校正錯誤并輸出診斷結果 |

輸出 |

輸出伴隨式S |

0/1 |

0/1 |

圖1為EDAC部分邏輯等效圖。

由于邏輯關系已經非常明確了,下面討論采用VHDL語言實現上述EDAC模塊的功能。可以有兩種方法來實現VHDL編程,即RTL級語言描述和行為級語言描述。其中RTL級描述的實現難度比較大,需要根據前面設計的邏輯功能,轉換為基本的門來描述;有效率高和受邏輯綜合軟件的影響小等優點,但可讀性差,實現起來比較困難。因此我們采用的是行為級描述,根據四個輸入作敏感量,用一個進程(process)就可以實現。編程思路是:根據控制端C0和C1進行判斷,如果是寫周期,直接將輸入的數據相應位進行異或后輸出;如果是讀周期,先生成伴隨式S,然后判斷S,用CASE語句執行相應的輸出。需要強調的是在不需要輸出的時候,要把輸出端用高阻封住。

利用這個EDAC模塊再輔以簡單的外圍電路就可以實現較強的EDAC功能,可以把這一部分整個電路都集成到FPGA中。

3仿真結果

仿真環境:MAX+plusII10.0。

仿真模擬器件:FLEX10K系列,EPF10K10LC84-3。

信號功能說明見表3。

表3仿真信號說明

|

信號名稱 |

功能說明 |

|

CLK |

模擬CPU時鐘,在該仿真中設定時鐘頻率為10MHz |

|

WRITE |

模擬CPU發出的寫信號 |

|

READ |

模擬CPU發出的讀信號 |

|

MEMW |

由EDAC電路發出的內存寫信號,主要用于數據糾正后的回寫 |

|

HIGH |

恒為高電平,提供芯片使能信號 |

|

INT |

EDAC電路檢測到兩個以上錯誤時發出的中斷請求信號 |

|

ERR |

EDAC檢測到錯誤時發出的信號,構校驗位產生一位錯誤時不產生該信號 |

|

CBIN[5..0] |

6位校驗位輸入 |

|

DBIN[15..0 |

16位數據位輸入 |

|

CBOUT[5..0 |

寫周期時作校驗輸出,讀周期時輸出為伴隨式S |

|

DBOUT[15..0 |

16位數據位輸出 |

(1)寫周期的仿真

圖2所示仿真圖中,275~500ns仿真了一個寫周期,數據輸入是AA55,而校驗位輸出是00,通過驗證是符合上面的設計邏輯的。

(2)讀周期的仿真

在讀周期的仿真中,我們模擬了以下四種情況。

①正確的讀周期:出現在650~975ns,校驗位、數據位都是正確值。

②數據位出現一位錯誤:圖2中1.25~1.65μs模擬了數據位產生一位錯誤的情況。數據正確的情況下應該是AA55,但現在d8位發生了錯誤,讀入的數據變為AB55,可以看出數據已經被自動更正為AA55;同時,ERR輸出"1"表明有錯誤發生,CBOUT輸出為23,即100011,從表1可以看出是d8位發生了錯誤。

③校驗位出現一位錯誤:圖2中1.8~2.0μs模擬了校驗位產生一位錯誤的情況。校驗位正確的情況下應該是00,但現在C2位發生了錯誤,讀入的數據變為04,可以看出數據沒變,仍為正確值AA55;同時,ERR沒有輸出,CBOUT輸出為04,即000100,從表一可以看出是C2位發生了錯誤。

④發生了兩位錯誤:圖2中2.4~2.75μs模擬了數據位產生兩位錯誤的情況。數據正確的情況下應該是AA55,但現在d8位和d0位發生了錯誤,讀入的數據變為AB54,可以看出EDAC電路已經無法自動更正。ERR和INT同時輸出"1"表明有多位錯誤發生,INT信號可以向CPU申請中斷,用中斷服務程序進行異常處理。

可以看出仿真結果可以滿足設計時的思想,能夠起到自動糾正一位錯誤和檢測兩位錯誤的功能。

結語

本文利用糾錯編碼的基本知識,提出了一種簡單實用的能自動糾正一位錯誤和檢查兩位錯誤的編碼方法,并且通過VHDL語言編程,用FPGA器件來實現。在我們自己的嵌入式系統中,EDAC電路已經得到了應用和驗證。現在越來越多的嵌入式系統對可靠性要求越來越高,采用EDAC技術可以簡單有效地提高系統的容錯能力;但針對不同系統,EDAC和CPU的時序配合可能會有所不同。例如,對于一些時鐘頻率比較高的CPU,可能需要插入等待周期等等,但由于采用VHDL語言進行設計,有很大的靈活性,稍加改動就可以滿足不同場合的需求