摘 要: 現(xiàn)場可編程邏輯門陣列(FPGA)應(yīng)用于圖像處理時(shí),需要對數(shù)據(jù)中的圖像信息進(jìn)行準(zhǔn)確的提取。設(shè)計(jì)中,F(xiàn)PGA中解壓縮功能需要對壓縮數(shù)據(jù)中的圖像信息進(jìn)行提取。根據(jù)壓縮格式,設(shè)計(jì)了一種基于狀態(tài)機(jī)的圖像信息提取模塊,并且在XST(Xilinx官方綜合工具)以及Synplify pro兩個(gè)綜合環(huán)境下進(jìn)行了仿真驗(yàn)證。通過對比仿真結(jié)果的差異,嘗試分析設(shè)計(jì)的寄存器傳輸級視圖(RTL視圖),并找出了影響狀態(tài)機(jī)工作的關(guān)鍵要素。強(qiáng)調(diào)了代碼風(fēng)格對FPGA設(shè)計(jì)的重要性。

關(guān)鍵詞: 現(xiàn)場可編程邏輯門陣列;狀態(tài)機(jī);XST;Synplify pro;代碼風(fēng)格

0 引言

狀態(tài)機(jī)是數(shù)字系統(tǒng)設(shè)計(jì)中的重要組成部分,是FPGA實(shí)現(xiàn)高效率高可靠性邏輯控制的重要途徑。在實(shí)際工程應(yīng)用中,狀態(tài)機(jī)工作是否正常決定著系統(tǒng)能否穩(wěn)定工作。本文設(shè)計(jì)了一個(gè)基于狀態(tài)機(jī)的圖像信息提取模塊,通過對該設(shè)計(jì)的仿真,分析了狀態(tài)機(jī)設(shè)計(jì)中的狀態(tài)競爭、鎖存器的引入以及綜合工具誤判等常見情況。強(qiáng)調(diào)了代碼規(guī)范對于FPGA設(shè)計(jì)的重要性。

1 設(shè)計(jì)背景及思路

基于相機(jī)的實(shí)時(shí)圖像目標(biāo)仿真系統(tǒng)可以產(chǎn)生實(shí)時(shí)的虛擬目標(biāo)圖像流,因而被用于光電經(jīng)緯儀等圖像跟蹤系統(tǒng)的開發(fā)調(diào)試。目標(biāo)仿真系統(tǒng)中虛擬目標(biāo)是經(jīng)過DSP以一定的壓縮格式壓縮后儲存于DDR中的,F(xiàn)PGA通過SRIO與DSP通信,讀取壓縮后的目標(biāo)圖形數(shù)據(jù),經(jīng)過FPGA內(nèi)部解壓縮與現(xiàn)實(shí)背景疊加輸出。該系統(tǒng)中使用灰度圖像作為圖像源。其簡化結(jié)構(gòu)圖如圖1所示。

目標(biāo)圖像示意圖如圖2所示,虛擬目標(biāo)圖形以水平方向的線段形式壓縮,整個(gè)壓縮后的目標(biāo)圖形由n條線段組成,每條線段包含該線段的起始行列號、像素點(diǎn)數(shù)以及各像素點(diǎn)的像素值。其中每一幀的第一條線段還包含這幀圖像壓縮后的大小,壓縮大小為32 bit。行列號、像素?cái)?shù)以及各像素點(diǎn)的像素值均以16 bit表示。

FPGA對虛擬目標(biāo)圖像進(jìn)行復(fù)原時(shí),最主要的是對壓縮數(shù)據(jù)中的目標(biāo)圖形的各類信息進(jìn)行提取,行列號代表著目標(biāo)圖形的位置信息,壓縮大小以及像素?cái)?shù)表示目標(biāo)圖形的大小信息,像素值則代表各點(diǎn)的灰度信息。本文以有限狀態(tài)機(jī)為基礎(chǔ)設(shè)計(jì)了基于狀態(tài)機(jī)的壓縮圖像信息提取模塊。

首先需要確定狀態(tài)機(jī)的狀態(tài)數(shù)。壓縮圖像信息提取模塊的目的在于將壓縮圖像的信息進(jìn)行分別提取,因此根據(jù)壓縮的數(shù)據(jù)格式須將數(shù)據(jù)分為5塊進(jìn)行提取,分別為一幀壓縮圖像大小(frame_size,32 bit)、每條線段的起始行號(row_no,16 bit)、起始列號(column_no,16 bit)、每條線段的像素?cái)?shù)(row_size,16 bit)以及分別的像素值(pic_element,16 bit)。考慮到16 bit的位寬,須將一幀壓縮圖像大小(frame_size)進(jìn)行兩次提取,由于空閑狀態(tài)的存在,共設(shè)置7個(gè)狀態(tài),分別為:wait_state(S0)、frame_s_state1(S1)、frame_s_state2(S2)、row_no_state(S3)、column_no_state(S4)、row_s_state(S5)、pic_element_state(S6)。

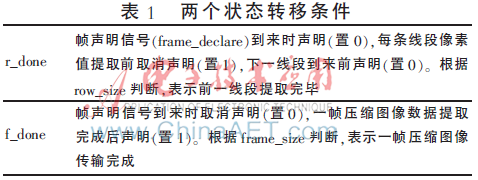

需要注意的是壓縮數(shù)據(jù)中frame_size只存在于第一條線段,因此frame_size的提取在一幀數(shù)據(jù)中只進(jìn)行一次。根據(jù)數(shù)據(jù)大小以及每行像素?cái)?shù),可以設(shè)置相應(yīng)的狀態(tài)轉(zhuǎn)移條件,相應(yīng)的信號如表1所示。

壓縮數(shù)據(jù)在幀聲明信號到來之后開始傳輸,當(dāng)幀聲明信號到來時(shí),狀態(tài)機(jī)進(jìn)入等待狀態(tài)(S0),隨后便開始依次提取第一條線段中的信息,包括幀大小的前16 bit,幀大小的后16位,行號、列號、像素?cái)?shù)(即依次進(jìn)入S1、S2、S3、S4、S5狀態(tài)),接著將r_done信號拉高,并且開始提取像素值數(shù)據(jù)(即進(jìn)入S6狀態(tài))直至下一線段到來,第二條線段到來時(shí)r_done信號拉低,提取第二條線段的行號(即從S6跳轉(zhuǎn)到S3狀態(tài)),其余步驟與第一條線段相同,直至一幀信號傳輸完成(即f_done拉高),狀態(tài)機(jī)跳轉(zhuǎn)置等待狀態(tài)(S0)。根據(jù)上述分析,狀態(tài)轉(zhuǎn)移圖如圖3所示。

2 綜合仿真

總結(jié)前面的分析,可以使用VHDL硬件描述語言對狀態(tài)機(jī)進(jìn)行描述。在VHDL設(shè)計(jì)中分3個(gè)進(jìn)程來設(shè)計(jì)狀態(tài)機(jī):(1)主控時(shí)鐘進(jìn)程,負(fù)責(zé)下一狀態(tài)與當(dāng)前狀態(tài)的切換,以及相應(yīng)狀態(tài)條件的邏輯部分;(2)狀態(tài)轉(zhuǎn)移組合邏輯進(jìn)程,根據(jù)當(dāng)前狀態(tài)及狀態(tài)條件進(jìn)行狀態(tài)轉(zhuǎn)移判斷并輸出下一狀態(tài);(3)同步時(shí)序狀態(tài)輸出,用同步時(shí)序邏輯寄存狀態(tài)輸出,避免組合邏輯的毛刺與不穩(wěn)定[1]。

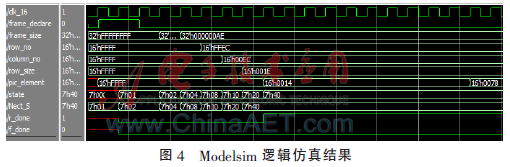

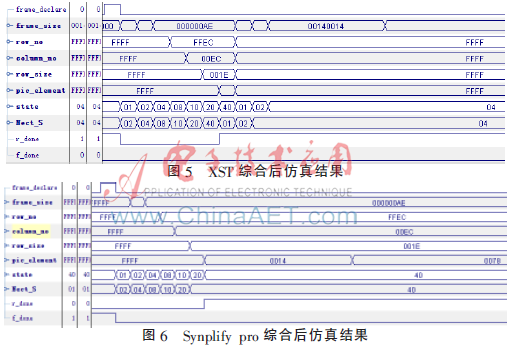

首先在Modelsim中對設(shè)計(jì)的代碼進(jìn)行了功能邏輯仿真。仿真結(jié)果與預(yù)期結(jié)果一致。仿真結(jié)果如圖4所示。

隨后對設(shè)計(jì)在XST和Synplify pro兩個(gè)綜合環(huán)境下進(jìn)行了編譯下載,并使用ChipScope進(jìn)行了板級仿真。使用的FPGA是Xilinx生產(chǎn)的Virtex5系列FPGA,型號為XC5VLX110T。圖5是XST綜合后的結(jié)果,圖6是Synplify pro綜合的結(jié)果。

同一個(gè)設(shè)計(jì)在不同綜合環(huán)境下出現(xiàn)了差異,XST綜合后的時(shí)序波形與預(yù)期不符,出現(xiàn)了錯(cuò)誤,而Synplify pro綜合后的波形則滿足了設(shè)計(jì)要求。這說明所設(shè)計(jì)代碼存在著問題。下面將嘗試著分析這些問題。

3 錯(cuò)誤分析

通過對代碼的分析,發(fā)現(xiàn)代碼存在很明顯的狀態(tài)競爭,以下面的代碼為例:

when S0=>

if r_done=′0′ and f_done=′0′ then

Next_S<=S1;

end if;

上面的代碼中if條件語句不完備,導(dǎo)致在!(r_done=‘0’and f_done=‘0’)時(shí)無法判斷下一狀態(tài),可能導(dǎo)致綜合工具產(chǎn)生誤判,并且可能引入鎖存器(Latch)來鎖存下一狀態(tài)[2]。而事實(shí)上,XST和Synplify pro的確都在設(shè)計(jì)中引入了鎖存器來保證狀態(tài)的正常切換和保持。這一點(diǎn)從綜合報(bào)告中可以看得出來。

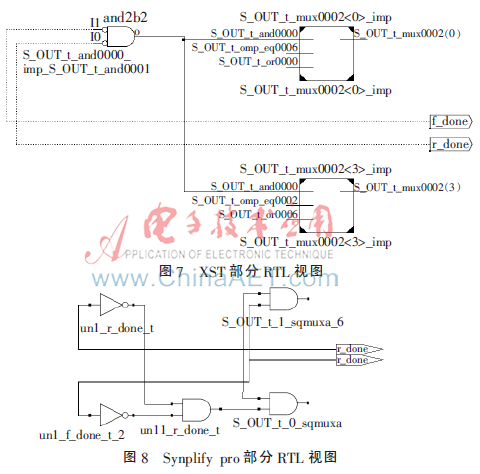

在兩者都生成鎖存器的情況下,認(rèn)為兩個(gè)綜合工具結(jié)果的差異,很有可能是因?yàn)榫C合工具的誤判。為了證實(shí)這一結(jié)論,本文嘗試著分析了XST和Synplify pro的綜合RTL視圖(寄存器傳輸級)[3-4],找出了兩者出現(xiàn)明顯差異的RTL視圖部分,如圖7、圖8所示。

圖7、圖8分別是XST和Synplify pro對下面這段代碼的綜合。

when S6=>

if r_done=′0′ and f_done=′0′ then

Next_S <=S3;

elsif r_done=′0′ and f_done=′1′ then

Next_S<=S0;

end if;

可以發(fā)現(xiàn)前者的判斷邏輯為:!r_done&!f_done 為真時(shí),狀態(tài)S6跳轉(zhuǎn)到S3;為假時(shí),狀態(tài)S6跳轉(zhuǎn)到S0。也就是說,在r_done=‘1’時(shí)狀態(tài)沒有保持S6,而是跳轉(zhuǎn)到S0,導(dǎo)致結(jié)果錯(cuò)誤。而后者的判斷邏輯為:!r_done&!f_done為真時(shí),狀態(tài)S6跳轉(zhuǎn)到S3,否則保持S6;f_done=‘1’時(shí),狀態(tài)S6跳轉(zhuǎn)到S0,否則保持S6。這個(gè)組合邏輯保證了在正常情況下,狀態(tài)機(jī)運(yùn)轉(zhuǎn)正常,因而得到了所希望的狀態(tài)輸出。

根據(jù)上面的分析,找出了兩個(gè)潛在的問題,鎖存器的引入以及綜合工具的誤判。顯然真正導(dǎo)致結(jié)果差異的是綜合工具對組合邏輯的誤判。但是在同步設(shè)計(jì)中鎖存器也常是一個(gè)潛在的問題。鎖存器不同于寄存器,鎖存器沒有時(shí)鐘驅(qū)動(dòng),對毛刺敏感,上電后處于不確定狀態(tài)。它會(huì)導(dǎo)致同步設(shè)計(jì)的時(shí)序分析復(fù)雜化,甚至出現(xiàn)時(shí)序以及穩(wěn)定性上的問題,通常這些問題都是不可復(fù)現(xiàn)的。另外FPGA的基本單元是由查找表和觸發(fā)器組成的,生成鎖存器反而需要更多的資源[5]。因此在同步設(shè)計(jì)中最好不要使用鎖存器[6]。

4 完善設(shè)計(jì)

根據(jù)先前的仿真與分析,對代碼中的狀態(tài)轉(zhuǎn)移條件判斷進(jìn)行了改進(jìn)和完備。解決的方式很簡單,就是完備if條件判斷語句,不至于讓綜合工具去猜測缺省的部分,從而避免綜合工具的誤判,同時(shí)也避免了鎖存器的引入。例如:

when S0=>

if r_done=′0′ and f_done=′0′ then

Next_S<=S1;

else

Next_S<=S0;

end if;

將修改后的代碼再次綜合,分別查看RTL視圖,發(fā)現(xiàn)XST和Synplify pro的RTL視圖中分別生成了XST和Synplify pro中表示有限狀態(tài)機(jī)的標(biāo)準(zhǔn)模塊[3-4],說明本文設(shè)計(jì)的狀態(tài)機(jī)是符合兩者要求的。對完善后的設(shè)計(jì)進(jìn)行了板級仿真,仿真結(jié)果與預(yù)期一致。

對比了修改前后Synplify pro綜合結(jié)果的時(shí)鐘性能和資源使用的情況,如表2所示。

5 結(jié)論

本文提出了一種基于狀態(tài)機(jī)的圖像信息提取模塊的設(shè)計(jì),并進(jìn)行了仿真分析。從上面的仿真分析可以看出代碼的設(shè)計(jì)風(fēng)格對于綜合結(jié)果的影響,綜合器作為設(shè)計(jì)工具,它的綜合優(yōu)化結(jié)果是依賴于代碼的。同一個(gè)邏輯,不同的代碼在綜合工具中可能產(chǎn)生不同的綜合結(jié)果,有的如同上面分析的Synplify pro,結(jié)果一致,但是性能差距很大;或者有些在結(jié)果上都不一致,如同上面分析XST一樣。因此對于一個(gè)FPGA設(shè)計(jì),初始設(shè)計(jì)思路是實(shí)現(xiàn)設(shè)計(jì)的關(guān)鍵,同樣實(shí)現(xiàn)設(shè)計(jì)的代碼語言風(fēng)格也對設(shè)計(jì)的結(jié)果有著重要的影響[7]。

參考文獻(xiàn)

[1] JAMES A R, GARY F G.VHDL設(shè)計(jì)表示和綜合[M].李宗伯,王蓉暉,王蕾,等譯.北京:機(jī)械工業(yè)出版社2008.

[2] 張巍,白天明,孟士超.XST綜合中的器件冗余及其程序優(yōu)化[J].計(jì)算機(jī)與數(shù)字工程,2009,37(5):181-184.

[3] Synopsys. Synopsys FPGA synthesis user guide[Z]. 2013.

[4] Xilinx. XST user guide for Virtex-4, Virtex-5, Spartan-3,and newer CPLD devices[Z]. 2008.

[5] Xilinx.Virtex-5 FPGA user guide[Z]. 2008.

[6] 王誠,薛小剛,鐘信潮,等.為什么XST與Synplify的綜合結(jié)果不一樣[J].中國集成電路,2003(50):54-61.

[7] LAU N. FPGA時(shí)序收斂一流設(shè)計(jì)讓您高枕無憂[J].賽靈思中國通訊,2010(35):15-18.