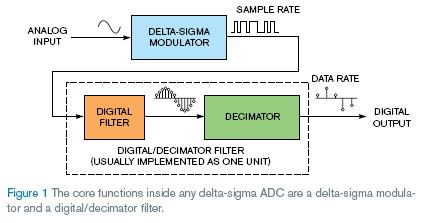

Σ-Δ轉換器在從直流到幾MHz信號的寬頻率范圍內,都能理想的實現高分辨率信號轉換。圖1顯示了Σ-ΔADC的基本拓撲或核心,其內部為Σ-Δ調節器和數字濾波器的串聯。研究Σ-ΔADC時,可以發現雖然它們具有多種特色,但都為這種基本架構。這個窗和后面的三個Baker最佳窗研究了基本拓撲和這兩個模塊的功能。

Σ-ΔADC的輸入信號為交流或直流電壓。這個和后三個Baker最佳窗使用單周期正弦波作為輸入信號。使用1位內部ADC,圖1中內部轉換調節器采集輸入信號,產生粗量化的輸出作為輸入信號。調節器將模擬輸入信號轉換為高速脈沖波形。調節器輸出脈沖序列一到零的比例反映了輸入模擬電壓。雖然調節器產生一個帶噪聲的輸出,但是未來的列說明電路將噪聲“塑造”成更高頻率的輸出頻譜。這個動作為數字濾波器輸出的低噪聲、高分辨率轉換鋪平了道路。

在調節器輸出,數字濾波器解決了高頻噪聲和高速采樣率的問題。因為信號位于數字域,可以采用低通數字濾波器削弱高頻率噪聲,采用抽取濾波器減小輸出數據的速度。數字/抽取濾波器采樣和濾除調節器1位代碼

串,并創建低速多位編碼。

雖然大多數轉換器只有一個采樣率,Σ-Δ轉換器卻有兩個:輸入采樣率和輸出數據率。這兩個有意義的變量比例定義了系統抽取比例。抽取率和轉換器有效分辨率之間存在一個強大的關系。未來的窗將檢測調節器、數字/抽取濾波器和可調節抽取比例怎樣工作。

英文原文:

Delta-sigma ADCs in a nutshell

Part one of a three-part series exploring the basic topology and functions of delta-sigma ADCs.

By Bonnie Baker -- EDN, 12/14/2007

MORE AT EDN.COM

Click here to read many more of this author's columns.

Delta-sigma converters are ideal for converting signals over a wide range of frequencies from dc to several megahertz with very-high-resolution results. Figure 1 shows the basic topology, or core, of a delta-sigma ADC, which has an internal delta-sigma modulator in series with a digital filter. As you explore delta-sigma ADCs, you will find that, although they have a variety of other features, they all possess this basic structure. This column and the next three Baker’s Best columns explore the basic topology and functions of these two modules.

The input signal to the delta-sigma ADC is an ac or dc voltage. This and the next three Baker’s Best columns use a single cycle of a sine wave as the input signal. Using a 1-bit internal ADC, the internal converter modulator in Figure 1 samples the input signal, producing a coarse, quantized output. The modulator converts the analog-input signal into a high-speed, pulse-wave representation. The ratio of ones to zeros in the modulator’s output pulse train mirrors the input-analog voltage. Although the modulator produces a noisy output, future columns will show that the circuit “shapes” this noise into the higher frequencies of the output spectrum. This action paves the way for a low-noise, high-resolution conversion at the output of the digital filter.

At the modulator output, the digital filter addresses high-frequency noise and high-speed-sample-rate issues. Because the signal now resides in the digital domain, you can apply a lowpass digital filter to attenuate the higher frequency noise and a decimator filter to slow down the out

put-data rate. The digital/decimator filter samples and filters the modulator’s stream of 1-bit codes and creates a slower multibit code.

Although most converters have only one sample rate, delta-sigma converters have two: the input sampling rate and the output-data rate. The ratio of these two meaningful variables defines the system’s decimation ratio. A strong relationship exists between the decimation ratio and the converter’s effective resolution. A future column will examine how the modulator, digital/decimator filter, and adjustable decimation ratio work.

Reference

Baker, R Jacob, CMOS Mixed-Signal Circuit Design: Volume II, John Wiley & Sons, 2002, ISBN: 0471227544.