1 引言

針對航天測試系統的應用需求,提出一種基于FPGA的微型數字存儲系統設計方案。該系統是在傳統存儲測試系統的基礎上,利用可編程邏輯器件FPGA對傳統存儲測試系統進行單元電路的二次集成,使測試系統體積大幅減小,功耗急劇降低,從而提高系統的抗高過載性能,增加系統靈活性、通用性和可靠性。FPGA不僅完成控制存儲及大部分的相關數字邏輯單元電路,而且使得整個存儲系統更為簡單,布線也更容易。另外,系統FPGA編程就是按照預定功能連接器件內的熔絲,從而使其完成特定邏輯功能的過程,一旦完成編程,FPGA就相當于一片能夠完成特定功能的集成電路,因而無需擔心程序運行路徑出錯,這與單片機有本質區別。

2 系統硬件設計

2.1 器件選型

2.1.1 電源轉換器TPS70358

系統中,FPGA工作電壓為3.3 V和2.5 V,USB接口器件CY7C68013 工作電壓為3.3 V,Flash工作電壓為3.3 V,系統需通過電源器件TPS70358將電壓轉換為3.3 V和2.5 V,為系統各器件提供電源。TPS70358是新一代的集成穩壓器,是一個自耗很低的微型片上系統,具有極低的自有噪音和較高的電源紋波抑制性能,因此,該器件適用于一塊電路板或一片重要器件(如FPGA、DSP)供電的電壓轉換。

2.1.2 現場可編程門陣列(FPGA)XC2S50

該系統采用XC2S50型FPGA控制各個接口,該器件是xilinx公司生產的Spartan II系列高性能現場可編程門陣列(FPGA),具有如下特點:內置標準JTAG接口,支持3.3 V在系統可編程(ISP);3.3 V電源,集成密度為50 000個可用門;引腳到引腳的延時7.5 ns,系統頻率高達200 MHz。采用單片FPGA實現邏輯控制功能簡化電路設計,提高系統可靠性。且XC2S50系統可編程,只需將一根下載電纜連接到目標板上,就可多次重復編程,方便電路調試。

2.1.3 USB 2.0控制器CY7C68013

CY7C68013是Cypress公司生產的一款USB 2.0控制器,該器件具有運算速度快、功耗小和性價比高等特點。時鐘周期高達40 MHz,每執行1條指令需4個時鐘周期;其內部集成有USB接口,I2C總線接口等,該系統設計實際數據傳輸速度高達10 MHz。

2.2 電路設計思路

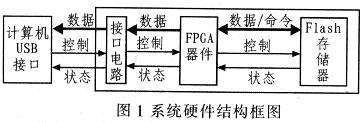

圖1為系統硬件結構框圖,計算機通過USB接口控制可編程邏輯器件FPGA實現對Flash存儲器的塊擦除、頁編程、讀數據等操作。

|

塊擦除操作時,計算機通過USB接口向FPGA發送指令,FPGA接收到指令后對Flash存儲器進行塊擦除操作,并將狀態返回計算機;頁編程操作時, FPGA接收計算機并行接口發送的指令,立即對Flash存儲器進行頁編程操作,先寫命令,再寫要編程的地址,然后將數據發送到Flash存儲器中;讀取數據操作時,FPGA首先接收計算機發出的指令,然后對Flash存儲器進行讀取數據操作,先寫命令,再寫要讀取的地址,然后開始輸出數據,并將狀態返回計算機并行接口。

3 系統軟件設計

3.1 FPGA對Flash的讀、寫、擦除操作

FPGA執行對Flash的讀、寫、擦除操作是利用VHDL語言的狀態機實現的。狀態機控制Flash的時序電路簡單易行,邏輯關系一目了然。XC2S50接收到CY7C68013傳來的擦除控制命令,立即執行擦除操作。按照時序,首先寫入自動塊擦除設置命令60H,之后依次寫入2個行地址和1個列地址進行尋址,而后寫入擦除命令D0H開始執行擦除操作。

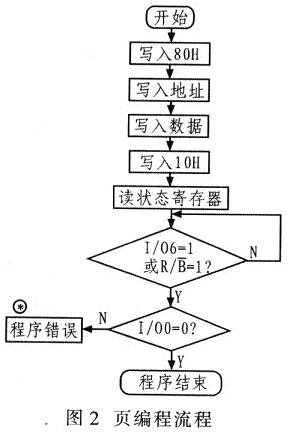

讀操作較為復雜,需要XC2S50和CY7C68013協同工作。這里只給出讀信號的操作過程。先寫人讀設置命令00H,因為讀一次執行一頁,所以地址的寫入是2個行地址和3個列地址,之后寫入讀命令,在等待rb變高后就可發送re信號將數據從Flash讀出。寫操作過程與讀操作類似,但寫操作完全由 XC2S50控制,寫完命令、地址后,開始寫入數據,直到寫滿2 KB數據,最后輸入頁編程命令。需要注意每寫完2 KB數據,Flash返回的狀態信號rb所等待的時間較長,大約是140μs。圖2為頁編程的流程。

|

3.2 CY7C68013控制邏輯及固件程序設計

CY7C68013主要完成兩部分工作,一是實現對擦除的控制開關命令,即上位機通過USB接口發送擦除命令,CY7C68013接收到這個命令后,會發送一個約為200 ms低脈沖通知FPGA啟動擦除操作;二是通過與FPGA配合,完成從Flash通過CY7C68013的GPIF接口讀入上位機的任務。 CY7C68013所用到的I/O包括控制線USBCTR1,狀態線US-BS0,讀信號線USBRD及8條數據線。