O 引言

開關電流技術是近年來提出的一種新的模擬信號采樣、保持、處理技術。與已成熟的開關電容技術相比,開關電流技術不需要線性電容和高性能運算放大器,整個電路均由MOS管構成,因此可與標準數字CMOS工藝兼容,可與數字電路使用相同工藝,并集成在同一塊芯片上,所以也有人稱之為數字工藝的模擬技術。但是開關電流電路中存在一些非理想因素,如時鐘饋通誤差和傳輸誤差,它直接影響到電路的性能。

本文詳細分析了第二代開關電流存儲單元存在的問題,提出了改進方法,并設計了延遲線電路。此電路可以精確地對信號進行采樣并延遲任意時鐘周期。解決了第二代開關電流存儲單元產生的誤差,利用此電路可以方便地構造各種離散時間系統函數。

1 第二代開關電流存儲單元分析

第二代開關電流存儲單元,在φ1(n-1)相,S1,S2閉合,S3斷開,晶體管M連成二極管形式,輸入電流ii與偏置電流I之和給柵源極間電容C充電。隨著充電的進行,柵極電壓vgs達到使M能維持整個輸入電流的電平,柵極充電電流減至零,達到穩態,此時M的漏極電流為:

![]()

在φ2(n)相,S1,S2斷開,S3閉合,此時輸出端電流為:

![]()

Z域傳輸函數為:

![]()

綜上可看出,晶體管M既作為輸入存儲管又作為輸出管,輸出電流i0僅在φ2相期間獲得。

2 延遲線

從結果來看,由于時鐘饋通誤差和傳輸誤差的存在,第二代開關電流存儲單元(以下簡稱基本存儲單元)輸出波形嚴重失真,尤其是級聯后的電路失真更加嚴重,無法應用到實際中,所以,設計延遲線電路。

電路原理如下:電路是一個由N+1個并聯存儲單元組成的陣列,且由時鐘序列控制。在時鐘的φ0。相,存儲單元M0接收輸入信號,而單元M1提供其輸出。類似的,在φ1相,單元M1接收輸入信號,單元M2提供其輸出。這個過程一直持續到單元MN接收其輸入信號,單元M0提供其輸出信號為止,然后重復循環。顯然,每個單元都是在其下一個輸入之前一個周期,即在其前一個輸出相N個周期(NT)之后,提供輸出信號。如取N=1,則延遲線是一個反相單位延遲單元,或連續輸入信號時,它是一個采樣保持電路,此時,延遲線電路和基本存儲單元相同。請注意,對于循環的N-1個時鐘相,每個存儲單元既不接收信號也不提供信號。在這些時刻,存儲晶體管上的漏電壓值變化到迫使每個偏置電流和保持在其有關存儲晶體管中的電流之間匹配。給出Z域傳輸函數為:

![]()

用基本存儲單元級聯延遲N個周期,則需要2N個基本存儲單元級聯,并且電路的時鐘饋通誤差和傳輸誤差會隨著N的增加越來越嚴重,到最后原信號將淹沒在誤差信號中。延遲線電路若要實現信號延遲N個時鐘周期,則需要N+1個并聯存儲單元組成,并且需要N+1種時序。由于這種電路結構不需要級聯,所以并不會像基本存儲單元級聯那樣使得時鐘饋通誤差和傳輸誤差越來越大。但是時鐘饋通誤差和傳輸誤差仍然存在,以下給出解決辦法。

3 時鐘饋通誤差及傳輸誤差的改善

3.1 時鐘饋通誤差的改善

改善時鐘饋通誤差可采用S2I電路。它的工作原理為:在φ1a相,Mf的柵極與基準電壓Vref相連,此時Mf為Mc提供偏置電流JoMc中存儲的電流為 ic=I+ii。當φ1b由高電平跳變為低電平時,由于時鐘饋通效應等因素造成Mc單元存儲的電流中含有一個電流誤差值,假設它為△ii,則Mc中存儲的電流為ic=J+ii+△ii。在φ1b相期間,細存儲管Mf對誤差電流進行取樣,由于輸入電流仍然保持著輸入狀態,所以Mf中存儲的電流為 If=J+△ii。當φ1b由高電平跳變為低電平時,考慮到△ii<

3.2 傳輸誤差的改善

傳輸誤差產生的原因是當電路級聯時,因為傳輸的是電流信號,要想信號完全傳輸到下一級,必須做到輸出阻抗無窮大,但在實際中是不可能實現的,只能盡可能地增加輸出阻抗。

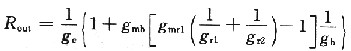

計算出輸出電阻為:

與第二代基本存儲單元相比,輸出電阻增大

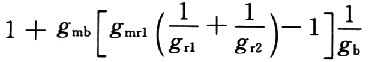

采用O.5μm CMOS工藝,level 49 CMOS模型對電路仿真,仿真參數如下:

所有NMOS襯底接地,所有PMOS襯底接電源,所有開關管寬長比均為0.5μm/O.5 μm。輸入信號為振幅50μA,頻率為200 kHz的正弦信號,時鐘頻率為5 MHz,Vref=2.4 V,VDD=5 V。表1中給出了主要晶體管仿真參數。

查看原圖(大圖)

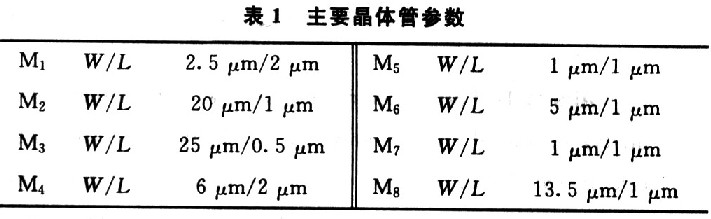

將原電路按照延遲線的結構連接并仿真,延遲3個時鐘周期(相當于6個基本存儲單元級聯),仿真結果如圖l所示。

查看原圖(大圖)

4 結語

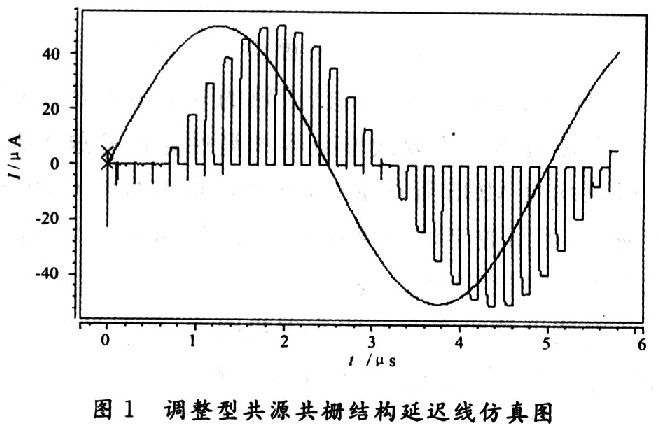

詳細分析了第二代開關電流存儲單元存在的缺點,提出了改進方法,并設計了可以延遲任意時鐘周期的延遲線電路,仿真結果表明,該電路具有極高的精度,從而使該電路能應用于實際當中。其Z域傳輸函數為

由于開關電流技術具有與標準數字CMOS工藝兼容的特點,整個電路均由MOS管構成,這一技術在以后的數模混合集成電路中將有廣闊的發展前景。

倍。結合S2I電路與調整型共源共柵結構電路的優點,構造調整型共源共柵結構S2I存儲單元。

倍。結合S2I電路與調整型共源共柵結構電路的優點,構造調整型共源共柵結構S2I存儲單元。

![]() ,在實際應用中,該電路可作為離散時間系統的基本單元電路。

,在實際應用中,該電路可作為離散時間系統的基本單元電路。