在數字信號處理領域,離散時間系統的輸出響應,可以直接由輸入信號與系統單位沖激響應的離散卷積" title="卷積">卷積得到。離散卷積在電子通信領域應用廣泛,是工程應用的基礎。如果直接在時域進行卷積,卷積過程中所必須的大量乘法和加法運算,一定程度地限制了數據處理的實時性,不能滿足時效性強的工程應用。本文從實際工程應用出發,使用快速傅里葉變換(FFT)技術,探討卷積的高速硬件實現方法。

1 卷積算法的原理

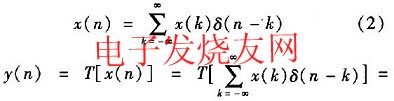

設線性時不變系統的沖激響應為h(n),則沖激響應和輸入δ(n)之間有關系

![]()

假設該系統的輸入為x(n),輸出為y(n),則根據線性時不變系統的定義,有

根據式(3),線性時不變系統的輸出信號可以由輸入信號與單位沖激響應的卷積求得。實際應用中,x(n)與y(n)的序列長度均為有限的,假設均為N,顯然,求出N點的y(n)需要N2次復數乘法,當序列長度大時,所需計算量是龐大,在需要實時處理的系統中,難以滿足實時性要求。

將M點序列x(n),L點序列h(n)分別作擴展,構造新的序列x’(n),h’(n),使得長度N滿足如下條件

根據時域循環卷積定理,x(n)與h(n)的線性卷積可以用循環卷積來代替。即

![]()

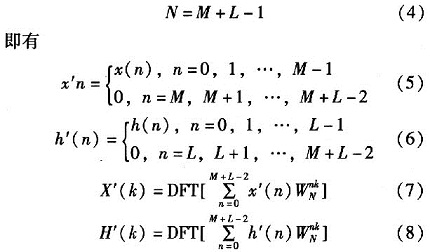

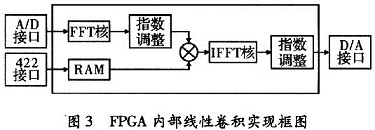

根據式(9),給出了一種基于快速傅里葉變換(FFT)的卷積的實現方法,如圖1所示。分別對補零后的z(n)和h(n)進行FFT運算,得到對應的頻域響應X(k)和H(k),將X(k)和H(k)相乘的結果再做IFFT,即可以得到x(n)和h(n)的卷積結果y(n)。

2 基于FPGA" title="FPGA">FPGA的高速卷積的實現

隨著電子技術的發展,現階段FFT硬件實現的方法主要有ASIC,DSP和FPGA這3類。專用FFT處理芯片ASIC,例如PDSPl6510,這類芯片的主要特點是技術簡單。但是由于此類ASIC處理點數有限,實現大點數FFT時,需要多芯片并行工作,會導致所需的配套控制復雜、存儲芯片較多,加大了系統實現難度。使用DSP,如TMS320DSP6416,控制程序設計比較簡單,但由于DSP的串行式軟件工作機理,當點數較大時,處理速度難以滿足實時要求。使用FPGA實現FFT功能,其并行處理機制允許FFT運算過程中使用流水線的形式,大大提高處理速度,而且隨著技術發展,FFT IP核技術日臻完善,使得基于FFT IP核的系統在速度、靈活性等方面均展現出優越性。本文使用Altera公司的StraTIx II系列芯片EP2S60實現線性卷積的功能。

Stratix II是Altera公司生產的一款高性能FPGA器件。它采用臺積電的90 nm工藝技術生產,等效邏輯單元(LE)最高可達180 kB,嵌入式存儲器容量最高可達9 MB。該器件不但具有較高的性能和密度,而且還針對器件總功率進行了優化,同時可以支持高達l Gb/s的高速差分I/O信號,因而是一款高性能的FPGA。該芯片中所含的高性能嵌入式DSP塊的運行頻率高達370 MHz。另外Stratix II還有12個可編程PLL,并具有完善的時鐘管理和頻率合成能力,能滿足高性能系統的需求。

EP2S60集成了60 440個等效邏輯單元(LES),內嵌M512 RAM模塊329個,M4K RAM模塊255個,M-RAM模塊2個,總存儲單元2 544 192 bit,并集成了DSP模塊36個、18 bit×18 bit嵌入式硬件乘法器144個,含有2個增強性鎖相環和8個快速鎖相環,可滿足本系統的要求。

3 FFT IP核的實現方法

為了節省開發時間,加速產品的投放,本文使用Ahera提供的FFT IP核來實現FFT和IFFT功能。Ahera FFT IP核函數是一個高性能、參數化的快速傅里葉變換(FFT)處理器,完全支持Ahera的FPGA系列。可以完成變換長度為2m(6≤m≤14)的基2、基4按照頻率抽選的高性能復數FFT以及逆FFT運算。

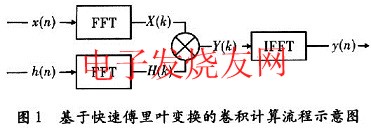

FFT IP核支持3種數據流模式,流模式(streaming)、緩沖突發模式(Buffered Burst)、突發(Burst)模式。并可以參數化設置變換點數和FFT或IFFT轉換方向。表l給出了FFT在Stratix II系列FPGA上使用流模式(Streaming)的性能。

為了在整個轉換計算過程中保持高信噪比,FFTIP核在定點結構與全浮點結構之間折中,使用塊浮點結構來表示轉換結果。在定點結構中,數據精度需要足夠大,才能充分表示整個計算過程中的所有的中間計算結果。在執行定點FFT過程中,經常出現數據的位數過大或精度損失的現象。而在浮點結構中,每個數用單獨的指數和尾數來表示,雖然這樣可以大大提高數據精度,但是浮點運算需要占用更多的器件資源。塊浮點結構保證了FFT整個轉換過程中數據位數的有效使用,每次通過基4-FFT運算以后,數據位數最大可能增加倍,根據前面輸出數據模塊動態范圍的測量進行比例換算,換算過程中累計的移位次數被作為整個模塊的指數輸出。這種移位方法保證了最低位(LSB)的最小值在乘法運算后的輸出進行舍入操作之前就被舍棄。實際上,塊浮點表示法起到了數字自動增益(AGC)的作用,為了在連續輸出模塊中產生統一的比例,必須用最終的指數對FFT函數輸出進行比例換算。

4 實際工程中的卷積的實現

如圖2所示,給出了一個實際應用的例子。為了保證I,Q兩路的相位同一性,使用雙通道A/D,選擇Linear公司的LTC2280,LTC2280支持10 bit,105 Ms/s的最大采樣率,并擁有61.6 dB的信噪比(SNR),85 dB的無雜散動態范圍(SFDR),滿足系統需要。雙通道D/A使用Analog公司的AD9763,AD9763支持10 bit、125 Ms/s的最大采樣率。

首先,需要在PC機上準備好h(n)對應的DFT變換結果H(k),H(k)的處理實際上有兩種方法,一個是將h(n)下載到下位機中,使用下位機硬件實現H(k),還有就是將H(k)在上位機就計算好,直接將計算結果下到下位機中。由于h(n)在系統工作中是不變的,在PC機端事先計算好H(k)更合適,不僅可以減少FPGA的資源占用,而且也方便數據的處理。基于以上的考慮,本系統將在PC機端求出的H(k)通過422接口下載到下位機的RAM中,方便使用。

下位機系統工作之前,上位機需要通過PCI控制板卡將計算好的數據下載到下位機的RAM中,方便工作過程中的數據使用。在收到外部控制信號后,下位機開始啟動,LTC2280開始采集I、Q通道數據并送入到FPGA中。

AD輸出的I,Q數據直接作為一個復數的實部和虛部進入FFT核進行FFT變換。為了加速處理速度,使用基-4四引擎輸出結構。FFT核輸出的結果X(k)過指數調整以后直接進入到一個硬件復數乘法器,與存儲于RAM中計算好的H(k)對應相乘,同時乘法器輸出可以直接輸入到IFFT模塊進行逆FFT運算,IFFT計算結果再經過指數調整以后即可以直接通過D/A輸出。

5 性能分析與改進

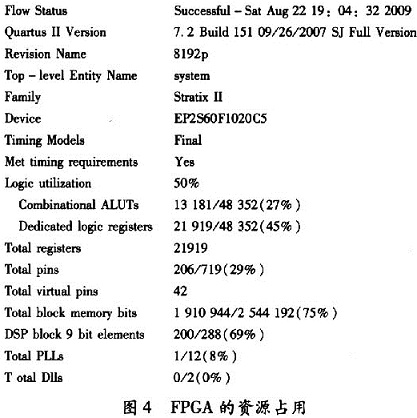

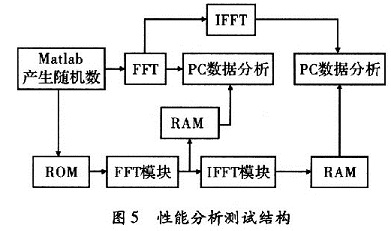

FPGA的流水線結構決定了速度的瓶頸取決于整個流程中處理速度最慢的部分。在FFT核速度可以保證的前提下(EP2S60的理論速度可以達到293.06 MHz),而處理過程中全部使用FPGA內部RAM來存儲中間數據,所以在本系統中,FPGA內部的理論處理速度達到200 MHz以上。本系統的處理速度主要局限于A/D和D/A的數據轉換率,根據實際測試,在100 MHz系統時鐘下,數據吞吐率可達100 Ms/s,滿足了設計技術指標。圖4給出了FPGA的資源占用。為了較好地檢測整個使用FFT_IFFT實現卷積的系統性能,設計了一個初略性能分析測試結構,如圖5所示。

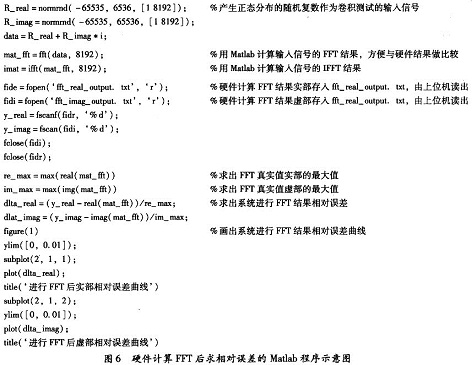

在圖5中,由上位機產生的一組8 192點隨機復數a(t)寫入ROM中,作為FFT模塊的信號輸入,經過FFT后將結果B(ω)存入RAM中,以方便上位機讀取并與a(t)使用Matlab計算出來的FFT結果A(ω)進行比較;接著將該FFT結果B(ω)再進行IFFT計算,由數字信號處理理論可知,一個信號進行FFT后再進行IFFT的結果應該是信號本身,所以將B(ω)再進行IFFT計算后得到的結果b(t)存入RAM,由上位機讀取并與原始信號a(t)進行比較,可以分析整個卷積系統的處理誤差。圖6給出了計算FFT結果相對誤差的Matlab相關程序。

求出A(ω)的最大值max[A(ω)],分別對B(ω)的實部和虛部計算相對誤差,得到如圖7所示的相對誤差曲線。由圖6可知,在FFT過程中,相對誤差可以保證在0.5%以內。對FFT所得的結果B(ω)做IFFT得到b(t),分析b(t)與原數據a(t)的誤差,得到如圖8所示的相對誤差曲線。

觀察圖8可知,經過FFT變換和IFFT變換以后的累積相對誤差保持在±3%以內,主要原因是FPGA計算FFT和IFFT過程中由于精度的要求,進行數據舍去,造成誤差的產生。這種誤差是由硬件客觀條件限制的,不可避免,但是±3%的誤差精度完全可以滿足實際應用。

本系統由于涉及到高速A/D、高速D/A,所以在PCB設計過程中必須考慮電磁兼容EMC(Electro MagneTIc Compatibility)和抗電磁干擾EMI(Electro Magnetic InteRFerence)性和信號的完整性。總體來說,在進行高速PCB設計過程中,不僅要考慮PCB的元器件布局和布線,同時設計中的接地、去耦和旁路同樣重要。例如在A/D部分這種混合信號PCB設計中,由于混合了模擬信號與數字信號,只有盡可能減小電流環路的面積才能降低數字信號與模擬信號之間的相互干擾。一個可行的方法是將地平面分割,然后在A/D轉換器下面將模擬地和數字地連接在一起。

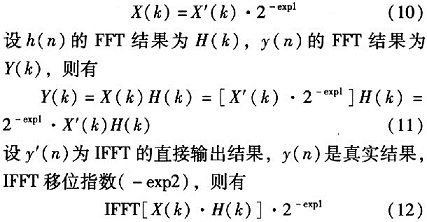

在處理FFT和IFFT核的指數問題時,正常做法是在FFT結束后直接做一次指數調整,在IFFT結束后再做一次指數調整。設經過FFT核后的直接輸出結果為X’(k)、對應指數輸出為(-expl),x(n)的真實結果為X(k),則有

由式(12)可知,FFT和IFFT的兩次指數調整實際可以在IFFT合為一次,可以減少控制的復雜程度。兩次調整指數的示意圖如圖9所示。一次調整指數的示意圖如圖10所示。

6 結束語

本文基于Altera的FPGA EP2S60F1 020C8,搭建了結合A/D,D/A等功能的配套處理平臺,完成了對高速離散卷積的硬件實現,使該系統在100 MHz時工作正常,滿足了設計要求。