摘要:為了改變人工神經網絡的研究僅僅局限于算法,只是在通用的串行或并行計算機上模擬實現(xiàn)的現(xiàn)狀,針對函數逼近問題,將BP神經網絡的結構分為3個模塊,采用VHDL語言完成對各個模塊的硬件描述,并使用Altera公司的QualtusII 6.1綜合軟件進仿真和調試,然后在Cyc-loneII系列FPGA上實現(xiàn)了能夠進行片上學習并完成函數逼近的BP神經網絡系統(tǒng)。測試結果證明,該系統(tǒng)能夠很好地完成在線學習,并能滿足一般系統(tǒng)應用的速度和精度的要求,驗證了該方法的有效性。

關鍵詞:神經網絡;硬件實現(xiàn);FPGA;片上學習;函數逼近

神經網絡是由大量的神經元通過特殊形式的加權網絡相互聯(lián)接而形成的,可以認為:神經網絡由兩種基本單元構成,即收集信號并且完成非線性變換的神經元胞,以 及完成各神經元之間的加權互連的突觸。標準的神經網絡VLSI的實現(xiàn)方式是在單個芯片上集成多個神經元和突觸單元,并且將它們按某種通信結構組成神經網絡 系統(tǒng),此外,還有基于ASIC結構的,針對神經網絡運算特點進行優(yōu)化和簡化設計的FPGA

實現(xiàn)方式,以及基于商業(yè)處理器(如數字信號處理、RISC單片處理等)的模擬神經網絡的多處理器結構的實現(xiàn)方式。

衡量一個神經網絡性能的重要指標是快速性和適用性,而FPGA的集成度已經達到百萬門級,用FPGA構造神經網絡時,可以靈活地實現(xiàn)各種運算功能和學習規(guī) 則,并且設計周期短、系統(tǒng)速度快、可靠性高、輸入輸出接口靈活、幾乎可以和任何形式的并行、串行接口及并行、串行A/D或D/A,DSP等連接,同時由于 可以將整個系統(tǒng)都集成在單個芯片內,因而抗干擾性能極強,使其在自動控制、故障診斷、模式識別,圖像獲取、DSP應用、嵌人式系統(tǒng)等領域有著廣泛的應用前 景。所以,F(xiàn)PGA無疑是首選的實現(xiàn)神經網絡的硬件芯片。

1 BP神經網絡的基本原理

BP人工神經網絡即誤差后向傳播網絡,是一種前饋網絡,由輸入層、隱含層和輸出層構成。隱含層通過作用函數執(zhí)行一種固定不變的非線性變化,將輸出空間映像 到一個新的空間,輸出層節(jié)點則在該新空間進行線性加權組合。BP算法用于多層網絡,對于線性情況,多層網絡可以簡單到只有一個輸入層節(jié)點和輸出層節(jié)點,而 沒有隱含層(中間層)。實際上,大多數自然、經濟和社會系統(tǒng)及其影響因素是非常復雜的非線性系統(tǒng),它不僅有輸入層節(jié)點及輸出層節(jié)點,而且還可以有一層至多 層隱含層節(jié)點。權值為零,說明相連的兩個神經元不發(fā)生作用,若為負,說明相連的兩個神經元之間相互抑制。此外,對于隱含層及輸出層的各神經元而言,它還有 一個閾值,其作用是調節(jié)神經元的興奮水平。當有信息輸入網絡時,該信息首先由輸入層傳至隱含層節(jié)點,經特性函數作用后,再傳至輸出層輸出,其間每經過一層 都要由相應的特性函數進行變換。節(jié)點的特性函數要求是可微的,通常選用S型函數,特性函數通常取Sigmoid函數,本系統(tǒng)選用Sigmoid函數,即![]() 和

和![]() 作為特性函數,具有較好的收斂性,模擬結論也比較符合實際情況。

作為特性函數,具有較好的收斂性,模擬結論也比較符合實際情況。

2 BP學習算法描述

BP網絡中每個節(jié)點都有一個狀態(tài)變量xi,節(jié)點i到節(jié)點j有一個連接權系數wji,每個節(jié)點都有一個閾值θj,每一個節(jié)點定義一個變換函數fj[xi,wji,θj(i≠j)],最常見的形式為

為了方便起見,將閾值θ作為神經元權值的第一個分量加到權值中去,那么輸入向量就應增加一項,可設輸入向量的第1個分量固定為l,這樣 的形式就可變?yōu)?img alt="e.JPG" border="0" src="http://files.chinaaet.com/images/20101206/fbe83be0-12ce-457d-928a-3d560f222b27.jpg" />。

的形式就可變?yōu)?img alt="e.JPG" border="0" src="http://files.chinaaet.com/images/20101206/fbe83be0-12ce-457d-928a-3d560f222b27.jpg" />。

一個3層單輸入、單輸出、n個隱節(jié)點的BP網絡結構如圖l所示。

圖1中,黑圓表示輸入為固定值1的神經元,用它與隱層神經元的連接權w011~w01n來表示隱層神經元的閾值,它與輸出層神經元的連接權w02來表示輸 出層神經元的閾值,w1I~w1n為輸入層到隱層之間的連接權值,w21~w2n為隱層到輸出層之間的連接權值。描述一個如圖1所示網絡的BP算法,它主 要包括2個階段:

1)正向傳播階段 從樣本集中取出一個樣本(x,d),計算隱層各個節(jié)點(神經元)輸出yI(i)=f(wl(i)x-w01(i))和輸出層節(jié)點輸出![]() 。

。

2)反向傳播階段 按下式反向計算各層節(jié)點的局部梯度δ和權值修正量 。

。

若激勵函數f選用單極性Sigmoid函數,則:

![]()

式中,x是輸入,d是期望輸出,f為激勵函數,η為學習率,δ(o)為輸出層節(jié)點的梯度,δi為隱層節(jié)點i的梯度。

3 BP神經網絡的VHDL設計

3.1 選擇系統(tǒng)處理數據字長

在運算中,涉及大量乘累加操作,本應采用浮點運算,但是占用的硬件資源和速度都將會不理想;如果采用定點運算,運算中帶來的“位增長”率將使每一級運算的 最大值可能會逐級加倍,因此如果不精心地規(guī)劃設計,這些值就會溢出,結果會因為精度不夠而無法使用。因此采用自定義的定點數進行基本的運算單元設計。本系 統(tǒng)采用不削弱神經網絡能力的最小要求16位(1,5,lO)帶符號定點數表示,最高位為符號位,低10位為小數位,其余為整數位。

例如:將1.5用16位(1,5,1O)帶符號定點數可表示為:0000011000000000,將-2.3用16位(1,5,10)帶符號定點數可表示為:10001 00100110011。

3.2 BP神經網絡模塊庫的建立

根據文件復用性的要求,建立基于VHDL語言的BP神經網絡元件庫,根據層次設計的要求,BP神經網絡結構的描述分為3層:第1層是前向 傳輸模塊的描述,包括輸入信號加權求和,權值的存儲和非線性激勵函數的實現(xiàn);第2層是反向傳輸模塊的描述;第3層是系統(tǒng)控制模塊的描述。下面用VHDL語 言對這3層結構分別進行設計。

3. 2.1 前向傳輸模塊的設計

圖2為前向傳輸模塊的VHDL程序設計流程。計算時x和w都是16位有符號數。相乘后為3l位數(最高位為符號位(兩輸入數符號位相異 或),低20位為小數位,其余10位為整數位),為了節(jié)省硬件資源四舍五入,舍去低10位小數位,為了防止后面相加是溢出,再擴展4位整數位,所以乘累加 后輸出為25位。

函數變換部分:對于FPGA硬件來說,其可實現(xiàn)的運算極為有限,而BP網絡中的作用函數sigmoid函數是非線性的,是硬件實現(xiàn)的一個難點,常用的實現(xiàn) 方法是查表法,這種方法比較簡單,但需要占用較多資源,當需要實現(xiàn)的網絡規(guī)模較大且精度要求較高時,查表法的實現(xiàn)有很大障礙;還有一個方法就是多項式逼近 法。本系統(tǒng)使用了查表和多項式逼近2種方法。

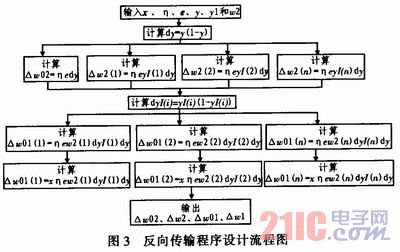

3. 2.2 反向傳輸模塊的設計

反向傳輸模塊的VHDL程序設計流程如圖3所示。

使用3輸入的乘法器計算△w02,4輸入的乘法器計算△w2.5輸入的乘法器計算△w01,6輸入的乘法器計算△w1,這樣并行計算△w02、△w2、△wO1、△w1。

3.2.3 系統(tǒng)控制模塊的設計

該系統(tǒng)控制模塊由一個計數器組成,計數器的輸入信號有:時鐘信號、啟動運算信號start、最大訓練次數maxcount、誤差信號e、 誤差容限eps,樣本數目;輸出信號有:前向傳輸控制信號enl,求誤差控制信號en2、反向傳輸控制信號en3、權值調整控制信號en4、權值讀寫信號 en5、讀樣本地址信號,訓練次數count。

3.3 基于FPGA的芯片和仿真軟件選型

芯片選型要考慮的因素有:硬件資源,例如LE個數、PLL個數、RAM個數;核心及外設電壓標準、功耗;軟件工具的功能對VHDL語言的支持;市場上專業(yè)開發(fā)板的支持。

本系統(tǒng)設計采用Altera公司Cyclonell系列的EP2C20Q240C8型FPGA。器件EP2C20Q240C8片內資源豐富,邏輯單元共18752個,最大用戶輸入輸出引腳為142個,器件EP2C20Q240C8還內嵌RAM,共208 KB,包含4個PLL,同時支持Nios軟核處理器。EP2C20Q240C8型FPGA的核心電壓是1.2 V,I/O電壓是3.3 V。而綜合軟件則使用Altera公司的QuallusⅡ6.1。

4 實驗驗證

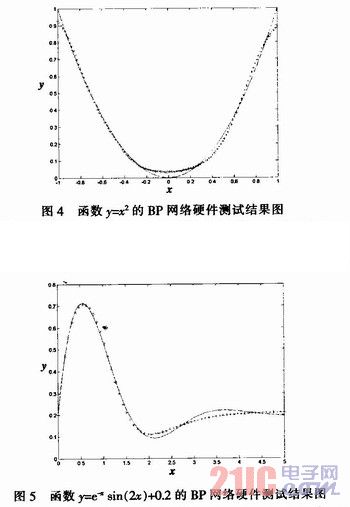

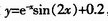

將該BP網絡用來實現(xiàn)函數逼近,取網絡為l-5-l(輸入、輸出層神經元數為1,隱層神經元數為5),本系統(tǒng)測試了很多函數,現(xiàn)將其中2例測試結果列出, 如圖4所示,(圖中實線為目標曲線,+線為逼近曲線)。由測試結果可以看出,對于函數中比較平坦的地方,該系統(tǒng)擬合結果不太理想,對于不同的網絡結構,網 絡模型的誤差或性能和泛化能力也不一樣,一般地,隨著網絡結構的變大,誤差變小。通常,在隱層節(jié)點數增加的過程中,網絡誤差會出現(xiàn)迅速減小然后趨于穩(wěn)定的 一個階段,因此,合理的隱層節(jié)點數應取誤差迅速減小后基本穩(wěn)定時的隱層節(jié)點數。合理網絡模型是必須在具有合理隱層節(jié)點數、訓練時沒有發(fā)生“過擬合”現(xiàn)象、 求得全局極小點和同時考慮網絡結構復雜程度和誤差大小的綜合結果。設計合理的BP網絡模型的過程是一個不斷調整參數的過程,也是一個不斷對比結果的過程, 比較復雜且有時還帶有經驗性。

例l:待測函數y=x2,測試結果如圖4所示。

例2:待測函數 ,測試結果如圖5所示。

,測試結果如圖5所示。

5 結論

以BP網絡為例提出了神經網絡硬件實現(xiàn)方法。應該說明的是:這種方法并非只適合于BP網絡,由于神經網絡都具有大規(guī)模并行的簡單運算的特點,所以可以將此方法推廣至更多類型的神經網絡。

本系統(tǒng)在參考前人工作的基礎上,綜合考慮了各種因素,用VHDL硬件描述語言設計并實現(xiàn)了該系統(tǒng),從測試結果來看,本文所設計的BP神經網絡不但達到了一 定的數據精度,也能滿足一般場合下的速度處理要求。此嘗試的成功將改變人工神經網絡的研究局限于算法和應用等領域的現(xiàn)狀,也必將極大促進神經網絡研究的進 一步發(fā)展,這也將推動神經網絡硬件在相關應用領域中的實用化。