摘要:為了實現便攜式、實時打印數據的目的,在分析EP3C25型FPGA和RD-E型微型打印機性能特點的基礎上,基于嵌入式技術設計了 FPGA與微型打印機的硬件接口電路、軟件流程及控制程序。利用FPGA控制微型打印機正常工作,對功能模塊進行了仿真,實際應用中運行穩定。利用 FPGA的穩定性與高速數據處理能力,實現實時打印。整個系統集成于一塊電路板,并由微型打印機輸出,體積小,攜帶方便。

關鍵詞:FPGA;微型打印機;硬件接口;軟件設計

0 引言

FPGA的超大規模集成度優勢和內部邏輯單元具有可重復配置能力的特點,使得其在芯片控制和接口設計中成為一種頗具吸引力的高性價控制器件。在此,設計了一種基于FPGA控制RD-E微型打印機工作的控制模塊。在QuartusⅡ9.0 FPGA開發平臺上通過VHDL語言編程控制微型打印機打印數據,在實際應用中具有一定的實用價值。

1 硬件系統

設計中采用Altera公司的CycloneⅢ系列FPGA芯片EP3C25和榮達創新科技有限公司生產的RD-E微型打印機組成硬件系統。

1.1 RD-E微型打印機簡介

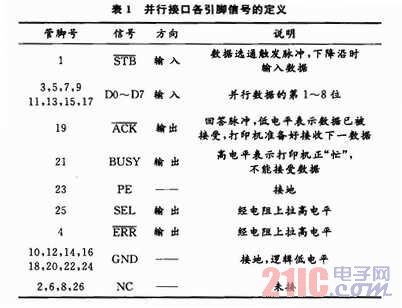

RD-E系列打印機是微型熱敏加熱點陣打印機,它專為儀器儀表面板安裝而設計,采用獨特的面板式嵌入結構,便可將整個打印機固定在儀表面板上。RD-E系列打印機內嵌448個字符及圖塊,32個用戶自定義字符,國標一、二級漢字庫中全部漢字和西文字、圖符共8 178個。采用模塊化驅動控制電路,有效地保護了打印頭的絕對安全;打印機內置專門的復位控制電路、電源監測電路以及近乎完美的軟硬件看門狗控制電路,以確保打印機不死機、不亂打。控制電路提供溫度檢測、電壓檢測、過熱檢測、缺紙檢測等功能,有效延長了打印頭的使用壽命,同時保證了打印機在不同的工作場合,打印出的效果更加清晰美觀、更加高速流暢,也能降低打印噪音,輸出完整數據。備有39個ESC/P兼容的打印命令,支持字符、漢字、圖形的正向、反向、左右旋轉打印、反白、上下劃線、左右劃線打印以及任意變高、變寬、行間距、字間距調整、水平制表、垂直制表、曲線打印、條形碼打印等功能以及以上功能的混合打印。RD-E打印機分標準并行接口,標準串行接口2類,串行接口與RS232C標準兼容,可直接由微機串口或單片機控制。設計中采用并口打印機,其接口與CENTRONICS標準并口兼容,其外形及從RD-E打印機的26芯插座的方向看插座的引腳序號如圖1所示。并行接口各引腳信號的定義如表1所示,信號的邏輯電平為TTL電平。

1.2 微型打印機與FPGA的接口設計

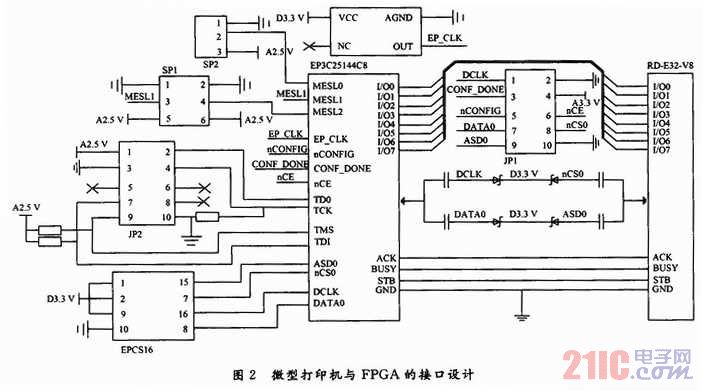

為滿足FPGA的工作條件,必須完成FPGA外圍電路的設計,如外部存儲器、工作電源以及外部輸入時鐘即晶振電路的設計。EP3C25E144I7 N是CycloneⅢ系列工業級FPGA芯片,其供電電源分數字電壓和模擬電壓兩類,其中模擬電壓有A1.2 V和A2.5 V,分別對其內部鎖相環PLL和模擬電壓端供電,數字電壓有D1.2 V和D3.3 V,分別對內部數字邏輯單元和輸入/輸出管腳供電。電源地同樣分為模擬地與數字地兩類,與模擬電源和數字電源對應。系統時鐘由外部晶振提供,配置方式由外圍電路撥碼開關選擇。

設計控制功能模塊時,由于FPGA有富余的I/O接口,所以打印機可以不經過另外的接口電路而直接與FPGA相連接,同時FPGA其內部的嵌入式陣列塊 EAB是輸入端口和輸出端口都帶有觸發器的RAM塊,可實現小容量的ROM和RAM,無需外部擴展ROM和RAM,也無需外加鎖存器。FPGA芯片可以通過編程配置其內部邏輯單元,通過編寫軟件來設計微型打印機控制器,所以只需分配好與打印機相連接的I/O接口,讀寫相連的信號線即可。打印機的BUSY,和D0~D7信號接口分別由FPGA在編程綜合過程中分配通用I/O接口,接口方式如圖2所示。

圖中JP1和JP2是FPGA的配置接口,JP1與EPCS16SI16N外部存儲芯片一起,構成FPGA的串行(AS)配置端口,當程序調試完成后,可將程序經JP2口下載至配置芯片EPCS16SI16N,FPGA上電之后,系統自動將配置芯片中的程序讀入FPGA內,完成邏輯功能塊的配置。JP1是 JTAG配置口,主要作用是方便程序的現場調試,不需經過外部存儲器,程序直接下載到FPGA中完成邏輯功能塊的配置,以驗證程序設計能否實現預期的功能。SP1與SP2用以設置配置芯片與FPGA數據傳輸的工作方式,例如MESL2,MESL1,MESL0為“010”時,配置為標準串行端口,配置電壓為3.3 V;若為“100”時為快速串行配置端口,配置電壓可在3.3 V和2.5V兩者中選其一。P1是有源晶振,可提供FPGA系統時鐘頻率。RP1是打印機數據端口的上拉排阻,這樣輸出數據與端口數據邏輯與之后輸入打印機,避免顯示亂碼。打印機RD-E32-V8與FPGA由8根數據線和3條控制、狀態讀寫線連接,另有一條線將2部分的接地端連接到公共的模擬地線。

2 軟件實現

系統軟件設計是基于VHDL語言編寫的。軟件設計的關鍵是在打印機工作時序的基礎上完成微型打印機與FPGA之間數據和指令的讀寫和狀態的檢測。

2.1 控制時序與原理

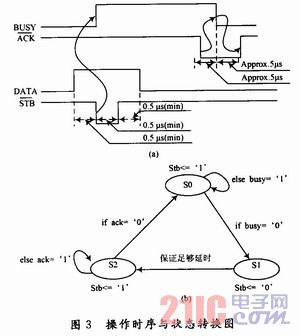

控制過程的時序在延遲時間上有嚴格的要求,所以,設計控制程序時,必須考慮打印機狀態轉換和數據傳輸的延遲時間。當數據線上有待打印的數據時,打印機并不是立即將數據打印輸出,必須根據當前的打印機狀態來判斷。

當BUSY狀態被檢測到為“1”時,說明打印機處于“忙”狀態,此時打印機不會接收任何數據。當BUSY信號為“O”時,說明打印機處于“空閑”狀態,先向數據線寫入數據,在延時時間符合時序的情況下,通過FPGA控制信號,將數據寫入打印機。為數據選通觸發脈沖,下降沿時輸入數據,對低電平的時間時序上也有要求,最小為O.5μs。當下降沿到來的同時,數據即送入打印機,同時BUSY信號由低電平跳變為高電平,阻止FPGA向打印機數據線寫入數據。當數據輸入以后,直到回答脈沖跳變成低電平,此時表示數據已被接受,而且打印機準備好接受下一數據,之后大約5μs時間以后,BUSY信號變為低電平,之后約5μs信號變高。對打印機的控制是通過查詢方式實現的,根據打印機工作時序,將打印機控制過程分為3個狀態,打印機控制程序基于這3個狀態,采用VHDL語言的有限狀態機編寫實現。時序與狀態轉換如圖3所示。

2.2 打印機控制命令及程序設計

RD-E型微型打印機提供了39條打印命令,打印命令與多數打印機兼容。其中,漢字打印命令其格式由16進制數表示,則為x“1B”x“3 8”x“n”。在連續3次接收數據后若接收到的是該命令,打印機將根據n值的不同選擇不同點陣的漢字。在漢字打印方式中,打印機接收的漢字代碼是2個字節對應一個漢字的標準機內碼,即打印機每接收2個字節的機內碼可調出一個漢字。打印機先接收機內碼的高位字節,再接收低位字節。設計中,由于欲打印的數據分 16×16和12×12兩種點陣漢字,所以n值設置為0或4,當n=O選擇16×16點陣漢字打印,n=4選擇12×12點陣漢字印,n的默認值為0。另一條命令是紙給進命令,即換行命令,其格式用16進制數表示為:x“OA”打印機打印當前緩沖器里的數據,并向前走紙一行,如果緩沖器里沒有數據,則只執行向前走紙一行。打印空格或空行命令,其格式用16進制數表示為:x“1B”x“6 6”x“M”x“n”。如果M=O,該命令將打印n個空格;如果M=1,該命令將打印n個空行。由于打印數據必須與表頭的欄目一一對應,而且每行打印的字符點陣不會完全相同,所以編程過程中對空格數的控制是需要花功夫的,調試時便出現過打印的已處理數據與表頭不對應的情況。由于打印機內嵌選擇字符集1和自定義字符集2,打印的數據中含有自定義字符集中的字符,所以還需選擇打印輸出字符集數據。字符集選擇由命令x“1B”x“36"和x“1B”x“37”來實現。回車命令的命令字為x“0D”。打印機收到本命令后,即對緩沖區內的命令和字符進行處理,并按要求打印緩沖區內的全部字符或漢字。

打印機內置的漢字代碼為標準漢字內碼,高字節數值范圍A1H~F7H,對應1~87區漢字;低字節數值范圍A1H~FEH,對應每一區中的漢字位碼1~94。漢字的區位碼與機內碼之間相互計算的方法為:

區碼轉換為16進制數,位碼轉換為16進制數

機內碼高字節=區碼+AOH

機內碼低字節=位碼+AOH

例如電阻的“阻”字區位碼為5572,即55區,第2個字,其機內碼為D7E8,將55(十進制)轉為37(16進制),37H+AOH=D7H;將 72(十進制)轉為48(16進制),48H+AOH=E8H,所以對表頭要打印的漢字將其區位碼轉換成內碼后存儲起來,按先高字節,后低字節的順序,在打印命令之后寫入打印機即可。

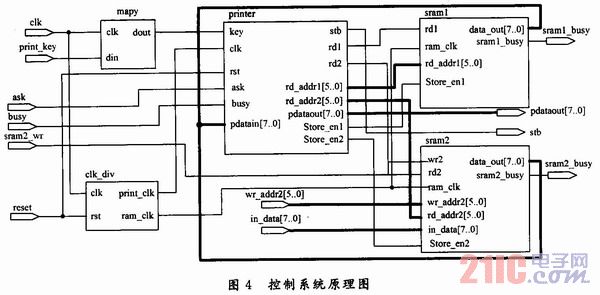

軟件設計在FPGA內部綜合生成2個內部存儲器,表頭數據存儲于一個存儲器中,對現場采集的數據獨立保存于另一個存儲器中,根據判別條件,由打印機控制模塊分時讀出存儲器的數據并寫入打印機顯示。控制系統原理如圖4所示。

圖4中,mapy模塊是按鍵防抖動模塊,clk-conv是時鐘分頻模塊,得到打印控制塊和隨機存儲器所需的時鐘。隨機存儲器SRAM1和SRAM2是利用FPGA內部資源綜合生成的,SRAM1中固化好了打印數據的表頭數據,只需控制讀即可。設計中為了編程方便,僅僅將SRAM2源碼稍作修改即生成 SRAM1,實際可以設計ROM代替。SRAM2用來存儲打印機前端數據采樣與處理單元處理的數據,并在打印控制模塊(printer)的控制下,分時送入打印機緩存。打印控制模塊是核心,它不僅查詢打印機的工作狀態,控制打印機打印緩沖區數據,還負責讀出SRAM中的數據,并寫入打印機。

2.3 系統功能仿真與分析

微型打印機控制塊(圖4中printer塊)的功能仿真圖如圖5所示。clk是系統時鐘,busy,ack,stb,dout是微型打印機的并行接口信號,currem_state表示工作時狀態之間的轉換關系。由圖可以看到,當busy=O時,狀態sO進入s1,系統對stb置位后,數據由dout輸出,狀態轉移到s2,s2有足夠的延時;當ack為低電平時,狀態轉移回到s0狀態,等待下一次數據傳輸。實際上數據在s1狀態時就應該輸出,但是圖中所示卻在s2狀態開始時輸出,這是因為設計有限狀態機時,采用的是莫爾狀態機的基本思想,它屬于異步輸出狀態機,輸出僅僅為當前狀態的函數,所以這類狀態機在輸入發生變化時還需要下一個時鐘的到來。打印機實際打印效果如圖6所示。

3 結語

利用VHDL硬件描述語言設計系統軟件,通過FPGA控制微型打印機工作。本微型打印機與FPGA組成打印系統后,FPGA將顯示數據寫入FPGA內部設計的SRAM中,FPGA與微型打印機進行數據交換后,將欲打印數據讀出并與控制命令一起按打印順序送到微型打印機打印緩沖區中,完成打印輸出。設計的打印系統攜帶方便,實時性高。