摘要:提出了基于電路分割技術實現通信系統發送端根升余弦波形成形濾波器查表法的FPGA結構,節省了ROM單元,討論了其ROM初始化時形波數據的組織方法,完成了該結構的VHDL實現,給出了該設計在Modelsim環境下的時序仿真結果。通過對仿真結果分析,表明所述的設計方法是可行的。該設計方案不隨波形樣本數目的增多而使電路系統變得更為復雜,它所實現的成形濾波器滿足于高速成形的應用需求。

關鍵詞:根升余弦;成形濾波器;查找表;FPGA

0 引言

數字通信系統中,基帶信號的頻譜一般較寬,因此傳遞前需對信號進行成形處理,以改善其頻譜特性,使得在消除碼間干擾與達到最佳檢測接收的前提下,提高信道的頻帶利用率。目前,數字系統中常使用的波形成形濾波器有平方根升余弦濾波器、高斯濾波器等。設計方法有卷積法或查表法,其中:卷積法的實現,需要消耗大量的乘法器與加法器,以構成具有一定延時的流水線結構。為降低硬件消耗,文獻提出了一種分布式算法(Distributed Arithmetic,DA)的濾波器設計結構。它將傳統的乘、累加運算轉化為移位、累加運算,當運算數據的字寬較小時,極大地降低了硬件電路的復雜度,提高了響應速度;當運算數據的字長較長時,因其需要更多的移位迭代運算而不適合高速處理的需求。為此,文獻提出了采用濾波器的多相結構與改進DA算法相結合的一種設計方法。當考慮ISI碼元數目較多時,該設計所需要的ROM表個數就會增多,同時訪問ROM所需的地址的產生電路就會變得更為復雜。文獻提出了采用存儲器分割技術,可以降低ROM單元的數量,但是它是以增加系統的復雜性與響應時延、信號毛刺為代價的。文獻在濾波器設計時采用了CSD編碼,雖然減少了乘法運算,但是需要設計CSD編解碼電路。

文中論述的是二進制基帶信號的連續查表法平方根升余弦波形成形濾波器(SRRC)的FPGA實現(滾降系數取0.22),取沖擊響應截斷時間為8T,每T內樣點數為8個,所用ROM單元數為2(8+3),每單元數據為16 b有符號整型數。查找ROM表所需11 b的地址由一個長8 b的數據移位寄存器與一個模8的采樣時鐘計數器鏈接而成。給出了設計在Modelsim 6.3下的時域仿真波形,經與理論相比較,文中的設計方法是可行的,且當二進制碼元的碼間干擾數增多(碼間樣點增加)時,地址電路簡單增長即可(不影響響應時間),便于FPGA的實現。

1 二進制基帶信號平方根升余弦成形原理

實際系統中,廣義信道傳遞函數H(f)由發送濾波器HT(f)、信道HC(f)、接收濾波器HR(f)三部分共同構成,即:

![]()

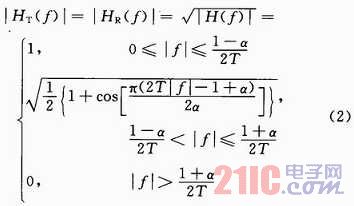

根據乃奎斯特第一準則,當H(f)幅頻特性滿足的滾降系數為α升余弦濾波器特征時,可以實現無ISI傳輸時刻降低對采樣時鐘精度的要求,當信道噪聲可以忽略時,取HC(f)≈1,按照接收濾渡器的輸出信噪比最大準則,有:

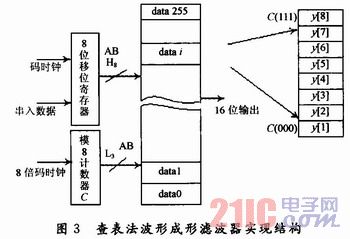

式中:T為輸入碼元的周期;α為滾降系數。記f0=1/(2T),由式(2)可推出滾降系數為α平方根升余弦沖擊響應為:

其時域響應如圖1所示。在數字化波形成形時,為確保h(t)采樣后的h[n]保持第一類線性相位,舍去h(t)|t=0樣點,同時對N(偶數)點h[n]右移N/2。文中采用的h(t)中t∈[-4T,4T],采樣間隔為T/8,于是,采樣后根升余弦成形濾波器的64個歸一化h[n]如表1 所示。

設發送端傳遞的二進制數據是{…,a-4,a-3,a-2,a-1,a0,a1,a2,a3,a4,a5,…},則發送濾波器的輸出如圖2所示,該波形函數可表示為:

![]()

可以看出,當前傳遞信息{a0}時刻對應的波形信號的上升沿y[1..8]分別由h-4[57..64],h-3[49..56],h-2[41..48],h-1[33..40],h0[25..32], h1[17..24],h2[9..16]與h3[1..8]線性表示,如式(5)所示:

2 二進制基帶信號平方根升余弦成形濾波器的FPGA實現

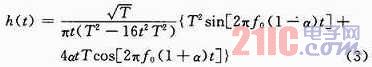

在分析文獻的基礎上,文中波形成形濾波器的實現采用的查表法結構如圖3所示。其中,ROM單元存儲待成形的數據與成形濾波器的沖擊響應的卷積結果。模8計數器的工作時鐘速率是待成形數據速率的8倍。待成形數據從8位移位寄存器的低位移入后,選擇ROM表中的數據塊da-ta i,同時模8計數器C從(000)2~(111)2計數,并用該計數結果C(j)選擇輸出data i中的y[j]。當計數器C計數歸零時,新的待成形數據從低位移入8位移位寄存器。該設計的一個優點是:ROM表中的數據在計算時,ai可采用雙極性碼,而查找表地址產生電路使用單極性碼。文中設計時,波形數據的計算采用了反邏輯、雙極性、不歸零碼,即輸入信息符號序列{0,1)映射為{+1,-1),持續時間不變。

2.1 連續查找表法的一種改進實現

由圖3不難實現采用本文的波形成形設計方案,共需要的ROM單元數目達2 048個。為此,可采用電路分割技術,將圖3所示的8位移位寄存器輸出的高8位地址同時給一個11位的中間寄存器,該中間寄存器的高8位又分為高4位與低4位,分別用于查找兩個各具有16個單元的ROM表,之后再將各自的輸出相加,此時消耗的ROM單元數共為256個。采用分割技術時,模8計數器、中間寄存器、ROM表三個部分的工作時鐘相同。

2.2 根升余弦成形濾波器的VHDL實現

文中所述濾波器是在Modelsim 6.3d環境下采用VHDL實現的。Quarts環境中以文本方式調用LPM_ROM宏功能模塊,定制ROM元件data_ rom_16,元件的地址寬度分別是4 b,輸出數據字寬同為15 b。加法器的輸出字寬16 b。實現的部分VHDL代碼如下:

![]()

2.3 Modelsim時序仿真結果

Modelsim環境不能直接對mif格式的ROM初始化數據進行仿真,應在QuartsⅡ環境下先打開mif文件,再另存為hex格式,然后在Modelsim環境下編譯后即可仿真。同時,如此操作又可將負值數據轉為補碼表示。Modelsim仿真結果如圖4所示,其中clk的周期為160 ns,正好是一個din碼元的寬度T,系統中地址產生電路的時鐘周期是20 ns,以確保在一個碼元持續時間內系統有8個樣點輸出。從圖4中發現,一個碼元成形后波形值延遲6T。

3 結論

文中所述的基于電路分割技術的查表法,實現通信系統發送端根升余弦滾降成形濾波器的FPGA實現方法簡單可行,且當截斷碼元數目增多時或碼內樣點數目增加時,僅通過改變地址移位寄存器的長度或計數器的長度與ROM的長度即可,不至于使電路的復雜度成倍增加。