摘要:給出了采用FPGA設計芯片技術對QPSK解調器進行設計的實現方法。該方法可將解調器中原有的多種專用芯片的功能集成在一片大規模可編程邏輯器件FPGA上,從而實現了高度集成化和小型化。仿真結果表明,該方案具有突出的靈活性和高效性,可為設計者提供多種可自由選擇的設計方法和工具。

關鍵字:差分解調;FPGA;π/4-DQPSK

0 引言

在現代移動通信中,使用較多的數字載波調制解調技術是多進制相移鍵控。π/4-DQPSK相位調制技術就是在常規DQPSK調制基礎上發展起來的,它的相位跳變值是π/4、3π/4,5π/4或7π/4,在DQPSK中,180°相位翻轉對應有豐富的功率譜旁瓣能量,限帶引起的包絡起伏將通過非線性功放的轉換效應導致可觀量值的頻譜擴散,從而使旁瓣干擾增大和限帶濾波作用抵消。與QDPSK相比,π/4-DQPSK限帶濾波后有較小的包絡起伏,其最大相位翻轉為135°,并在非線性信道中有更優的頻譜效率。而軟件無線電作為解決通信體制兼容性問題的重要方法,現已受到各方面的注意。該方法的中心思想是以硬件作為無線通信的基本平臺,而把盡可能多的無線通信功能(如工作頻段、調制解調類型、數據格式、通信協議等)用軟件來實現。而FPGA器件可反復編程,重復使用,因此用其實現調制解調是實現軟件無線電的一個重要環節。

1 π/4-DQPSK的基本原理

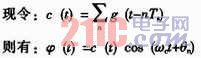

π/4-DQPSK數字基帶調制信號的數學表達式為(假設載波初相為0):

![]()

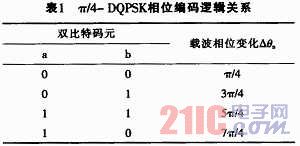

這里,g(t)是持續時間為Ts的矩形脈沖,θn為受調相位。表1所列是π/4-DQPSK信號的相位編碼邏輯關系。

2 π/4-DQPSK的解調

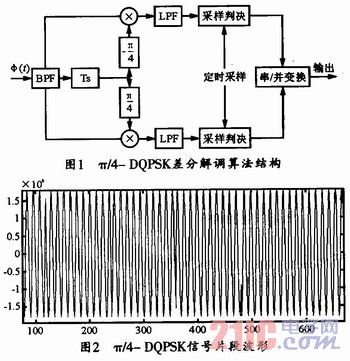

對于差分相干解調,通過比較前后碼元載波相位,便可分別檢測出A和B。然后用圖1所示的方法還原成串行二進制數字調制信號。

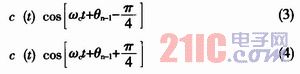

設某一碼元及前一碼元載波為:

![]()

那么,將AD采樣輸入FPGA中的π/4-DQPSK波形所圖2所示。

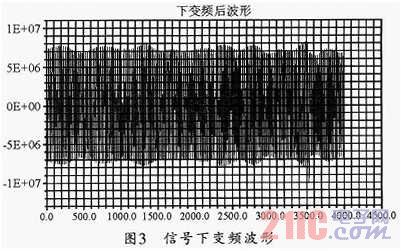

經過混頻后進入解調器的信號φ(t)的波形如圖3所示,設上支路為A,下支路為B。那么,經延遲移相后,其上、下兩支路分別為:

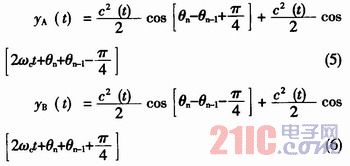

而乘法器的輸出為:

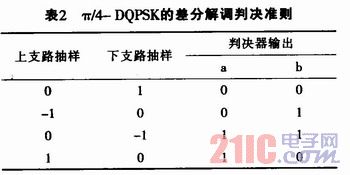

其A、B支路的乘法器輸出波形如圖4所示。表2所列為π/4-DQPSK的差分解調判決準則。

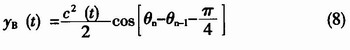

下面是A、B兩路乘法器的LPF輸出:

![]()

3 結束語

π/4-DQPSK差分解調算法的所有部分均可由VHDL編程實現。目前,整個過程已經經過功能仿真和時序仿真,并用OUARTUS II進行了綜

合、映射、布局布線,現已成功下載到Cyclone II中運行。可滿足預期的設計目標。該方案實現簡單,速度快,占用硬件資源少,非常適合工程應用。其軟件和硬件相結合的方法還具有體積小、功耗低、集成度高、可軟件升級、抗干擾能力強等特點,符合未來通信技術發展的方向。