摘 要:利用自動化綜合工具Design Compiler,采用Top-down的方法,對設計進行了綜合,實現了HDTV芯片的設計優化。設計重點考慮了時鐘安排、代碼的可綜合性和綜合的劃分。方案中利用綜合工具實現對HDTV芯片的優化,延遲優化到0.11的結果達到了設計的要求。

引言

--- 作為一種大眾傳播的媒介,高清數字電視(HDTV)以其極高的圖像質量和豐富的圖像表現力正成為未來信息媒介的核心。實現HDTV的各種芯片是目前集成電路設計的競爭熱點。

本文首先介紹利用自動化綜合工具在編碼和綜合的階段完成用于HDTV芯片設計的優化。由于Verilog代碼的好壞會直接影響到綜合的結果,所以在設計代碼的階段就應該把綜合的要求考慮進去。其次介紹該HDTV芯片的特點和結構,重點考慮HDTV芯片的結構復雜導致綜合的困難及解決方法。最后,介紹了如何把HDTV芯片用綜合工具Design Compiler將設計優化,使延遲從-0.94降到0.11。

VerilogHDL綜合性設計

1 時鐘安排

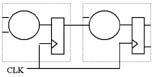

選用上升沿觸發的單時鐘信號,盡量不使用混合觸發的時鐘信號。因為時鐘周期在時序分析的過程中是關鍵問題,它還影響到時鐘的頻率。使用簡單的時鐘結構利于時鐘信號的分析和保持,避免在時鐘信號上添加buffer,還利于得到更好的綜合結果。圖1給出了上升沿觸發的單時鐘信號結構。

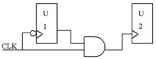

盡量避免使用門控時鐘。時鐘門控電路通常與工藝和時序有關,錯誤的時序關系會導致錯誤的時鐘和脈沖干擾。時鐘的skew會導致hold time的混亂,如圖2所示。此外,門控時鐘會使設計的可測試性下降。

同時,要避免使用內部的寄生時鐘和寄生reset。寄生時鐘不能作為掃描鏈的一部分,所以會使設計的可測試性下降,綜合約束的設計難度提高。只有一些低功耗的設計需要門控時鐘,在頂層模塊中注意要把時鐘或reset電路作為分立模塊。

2 綜合代碼

使用可綜合的代碼可以提高電路的可測試性,簡化靜態時序分析,使門級的電路和初始的寄存器級代碼功能一致。

利用寄存器代替組合邏輯的反饋,避免使用鎖存器(Latches)。寄存器受到時序邏輯的青睞,它可以維持一致性和綜合的正確性。在設計中用reset信號來初始化寄存器的信號。在Verilog中不要使用initial語句對信號進行初始化。

在每個always塊中,指定完整的敏感信號列表。如果不指定完整的敏感信號,行為級的前端綜合和后端綜合網表的結果會不符。綜合工具在elaborate設計時會給出警告。若增加多余的敏感信號則會降低仿真的速度。另外,注意阻塞性賦值和非阻塞性賦值的問題,阻塞性賦值一般用于時序電路中。

Case語句相當于一個單層的多路器;If-then-else語句相當于一個層疊的組合多路器。單一多路器的速度會快一些,所以通常建議使用case語句。避免使用full-case 和parallel_case,這兩種語句會導致在仿真和綜合過程中代碼的解釋出現差異。

編寫時序邏輯的代碼要包括狀態機和一個時序的進程,通過在進程外用assign語句來生成復雜的內部中間變量從而改進代碼的可讀性。使用define語句來定義狀態向量。把有限狀態機和非有限狀態機放在不同的模塊中有利于綜合。

在RTL代碼中不要使用任何延遲常量。延遲量不僅會導致在一些環境中的不正確,還會使得仿真和綜合的結果不一致,擾亂RTL仿真器代碼的優化。

3 代碼劃分

為了得到更好的綜合結果,更快的綜合速度,用簡單的綜合策略來滿足時序的要求,推薦使用以下綜合劃分的技術。

● 所有模塊都使用寄存器輸出。對于每個設計的子模塊都要記錄所有的輸出信號,這樣可以簡化綜合的過程并可預測輸出的驅動能力和輸入的延遲。

● 把局部的相關聯的組合邏輯放到同一個模塊中,對于有不同目標的設計應放在不同的模塊中。例如在綜合的過程中,把需要優化面積和速度的關鍵路徑邏輯放在分開的兩個模塊中,如圖3所示。

● 綜合時間的劃分最主要的標準是邏輯功能、設計目標、時序和面積的需要。準確的時序計算和適當的約束對綜合時間的影響遠遠大于電路規模的影響。把同一設計目標的電路邏輯放到一起也會減少綜合時間,而設計的約束過多會增加綜合時間。減少綜合時間的關鍵是在設計之前制定精確的時間預算,并使設計的宏模塊達到預算的要求,然后編寫綜合約束來滿足預算,最后是運用綜合工具的命令來實現約束。

● 避免時序異常。時序異常主要包括multicycle path和false path。如果設計中一定要用到多周期路徑,應記錄開始和結束點來確保在芯片級的有效。盡量避免使用異步邏輯,異步邏輯會給設計的正確性和驗證帶來困難。

● 注意glue模塊的放置。將頂層的連接模塊放到底層模塊中,同時確保頂層含有I/O管腳和時鐘發生器,如圖4所示。

HDTV芯片的特點

所設計的芯片應用了數量眾多的不同類型的RAM,其中包括內部1個單口RAM、2個雙口RAM、3個ROM和20個寄存器堆棧。

芯片內部要求多時鐘信號(27MHz、74MHz、150MHz),并通過clock mux來選中時鐘。27MHz時鐘用于dma模塊中的PCI總線時鐘,同時它和74MHz時鐘通過模式選擇來確定是HDTV模式還是SDTV模式的解碼。Pll核心時鐘頻率為13.5MHz,Pll輸入時鐘經過11倍頻后產生148.5MHz時鐘,pll時鐘同時也用于測試。此外還有6個驅動外部芯片的輸出時鐘,即PCI時鐘、視頻時鐘、2個SDRAM時鐘和2個SRAM時鐘。

為了得到較高的測試覆蓋率,本設計使用多種測試方法,如掃描鏈(scan chain)、邊界掃描(boundary scan)和存儲器的內建自測試(Bist)等。本設計多數模塊采用BIST方法達到測試目的,采用的是Mentor Mbistarchitect工具來自動插入BIST代碼。其他部分用Mentor Jtag工具來實現邊界掃描,插入JTAG代碼。

芯片外部與高速的SDRAM和SRAM的連接,每個模塊都包括4片RAM。HDTV芯片主要通過sdr_ssr_sel信號來實現兩種環境的轉換。

如圖5所示,HDTV芯片的結構設計方案層次復雜,芯片主要分為三層,其中core_top是不依賴于工藝的,它的主要功能是完成HDTV碼流的解碼。

如上所述,芯片的這些特點給后端的布局布線提出了很高的要求,綜合結果會直接影響布局布線(floorplanning),因此綜合的方法很重要。

綜合方案

1 初步綜合

首先把設計進行粗略的Top-down綜合,查看綜合結果報表。根據PDK的數據設置基本的Design Rules和Design Constraints。包括Setting Design Environment(Fanout load,Output load,Input drive impedance)和Setting Design Constraints(Design Rules Constraints (max_transition, max_fanout, max_capacitance),Timing Constraint (max_delay, min_delay),Area Constraint)。經過初步綜合后延遲的結果如表1所示。

表1給出的slack=-0.94是在沒有考慮wireload的情況下的結果,所以還需要很大改進。

圖6是綜合后用design_vision對critical path進行統計,得到的path slack分布結果。

2 基本解決方案

根據上述統計結果,得到core-top模塊不滿足時序要求的critical path最多,所以要通過把core-top模塊單獨進行優化來得到更佳的綜合結果。首先設置Design Environment和Design Rules,然后對延遲進行優化。

Design Compiler對設計的時序優化是基于所指定的延遲約束進行的。影響延遲的約束包括時鐘、輸入和輸出延遲、外部負載、輸入單元的驅動能力、運行環境和線負載模型等。解決延遲問題的具體方法如下。

● 使用set_false_path命令。包含兩個以上時鐘的設計中,在沒有關聯的時鐘之間要設置false路徑,否則就會浪費更長的運行時間和更高的內存占用率。

● 使用ungroup命令,拆分底層模塊。

● 用set_critical_range命令定義關鍵路徑的優化范圍。

● 用set_cost_priority-delay命令設置延遲的優先級高于設計約束的優先級。

● 用set_ultra_optimization命令,可以用調用邏輯復制和門映射的算法來編譯。

● Compile incremental命令是在原有的綜合的基礎上,改進設計中不滿足約束的部分,保留滿足約束條件的部分。

● Compile-map_effort-high命令中,-high與-medium和-low相比需要編譯時間更長,但是能得到更佳的綜合結果。這個設置可以使關鍵路徑再次綜合。

3 綜合結果

圖7給出三步對延遲進行優化的結果,實現的具體步驟如下。

首先,依據報表查出延遲產生的原因。根據報表把主要的三個時鐘之間設成false_path,根據前端coding階段的設計設置multicycle,加上下面約束生成新的報表。

Ungroup

Set_critical_range 5

Set_cost_priority -delay

Set_ultra_optimization

Compile incremental

通過設置錯誤路徑和多周期后,由新的報表可以得到path slack減少到了 -0.50。

然后,使用compile-map_effort high命令。根據報表path slack="-0".36,結果還需要進一步優化。

從報表可以看出slack不滿足的路徑主要集中在視頻模塊中的時鐘信號ve_clk、PCI模塊中的pci_clk,以及RAM模塊中的sdr_clk0、sdr_clk1、ssr_clk0和ssr_clk1,所以需要給以上路徑增加false_path 。Video_mode_reg模塊是一個存儲狀態值的模塊,寫入后不再改變,所以也設為false_path。最終結果path slack="0".11,滿足要求。

如果slack是由兩個模塊產生而不是模塊內部的問題,還可以用ungroup命令拆分。本結果的slack就是由ve_mem模塊內部產生,但結果的slack已經滿足了要求,而且經過后端處理會改進的更好。

結束語

本文對HDTV芯片,從編碼和綜合兩個方向入手,提出了解決方案。通過使用Synopsys公司的綜合器Design Compiler,采用Top-down的方法對設計進行綜合。結果表明綜合方案較好的滿足了綜合目標,效果明顯。