關(guān)鍵詞:Verilog HDL;改進(jìn)Booth算法;乘法器;

1 引言

Verilog HDL是當(dāng)今最為流行的一種硬件描述語言,完整的Verilog HDL足以對(duì)最復(fù)雜的芯片和完整的電子系統(tǒng)進(jìn)行描述[1]。本文采用Verilog HDL語言來設(shè)計(jì)實(shí)現(xiàn)4-2和5-2混合壓縮器構(gòu)成的乘法器的設(shè)計(jì),并與另外實(shí)現(xiàn)的兩種乘法器從速度,面積和硬件資源占用率等方面進(jìn)行了性能比較,得出用這種改進(jìn)壓縮器要比兩位陣列乘法器和傳統(tǒng)的4-2壓縮器構(gòu)成的乘法器速度提高了10%,硬件資源占用減少了2%。

2 兩位陣列乘法器

陣 列乘法器基于移位與求和算法。兩位陣列乘法器是對(duì)乘數(shù)以2bit進(jìn)行判斷,這樣可以在部分積的數(shù)目上比一位判斷陣列乘法器減少1倍;另外,陣列乘法器結(jié)構(gòu) 比較規(guī)范,利于布局布線,但是陣列乘法器存在進(jìn)位問題,運(yùn)算速度比較慢,所需時(shí)鐘周期長,時(shí)延大。以下是兩位判斷的乘法器的Verilog HDL語言部分程序:

module imult _radix_2(prod,ready,multiplicand,multiplier,start,clk);

……

case ( {product[1:0]} )

2'd0: pp = {2'b0, product[31:16] };

2'd1: pp = {2'b0, product[31:16] } + multiplicandX_1;

2'd2: pp = {2'b0, product[31:16] } + multiplicandX_2;

2'd3: pp = {2'b0, product[31:16] } + multiplicandX_3;

……

3 改進(jìn)Booth編碼乘法器

陣列乘法器雖然占用相對(duì)較少的硬件面積,可是運(yùn)算速度非常慢,不能滿足高速運(yùn)算的要求。為了得到高速的乘法器,可以從兩個(gè)方面來提高乘法器的計(jì)算速度:減 少部分積數(shù)目;提高部分積壓縮速度。通常減少部分積數(shù)目采用二階的Booth編碼實(shí)現(xiàn);可用4-2壓縮器構(gòu)成的Wallace樹來提高部分積求和速度。本 文采用4-2壓縮器和5-2壓縮器的混合Wallace樹來進(jìn)一步提高求和速度。www.51kaifa.com

改進(jìn)Booth算法通過對(duì)二進(jìn)制補(bǔ)碼數(shù)據(jù)重新編碼,壓縮PP(部分積)數(shù)目,以提高運(yùn)算速度。其中,壓縮率取決于編碼方法,如果采用三位編碼,可壓縮 1/2的PP,再對(duì)所得的n/2個(gè)部分積進(jìn)行求和運(yùn)算。在電路實(shí)現(xiàn)中還可采用混合握手協(xié)議和管道傳輸方式,可以降低電路的功耗,僅占Amulet3i乘法 器的每次運(yùn)算的能量消耗的50%【2】,另外,也可以采用混合邏輯乘法器設(shè)計(jì)【3】。Booth算法電路圖在文獻(xiàn)[4]中有具體介紹。

3.1 4-2壓縮器

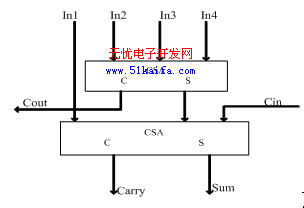

4-2壓縮器使用2個(gè)CSA(Carry-save Adders保留進(jìn)位加法器),將5個(gè)數(shù)據(jù)(4個(gè)實(shí)際數(shù)據(jù)和一個(gè)進(jìn)位)相加產(chǎn)生3個(gè)數(shù)(Sun, Carry和Cout)。4-2壓縮器結(jié)構(gòu)圖如圖1所示【4】。

圖1 由2個(gè)CSA構(gòu)成的4-2壓縮器

4-2壓縮器是進(jìn)行部分積壓縮最常用到的部件,與全加器相比,具有電路簡(jiǎn)單、連線規(guī)則的優(yōu)點(diǎn).傳統(tǒng)4-2壓縮器輸入與輸出的邏輯關(guān)系表達(dá)式[8]為:www.51kaifa.com

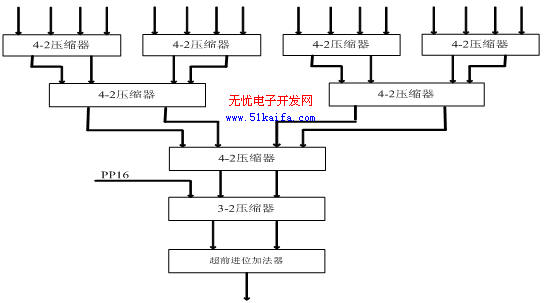

表達(dá)式中:In1~I(xiàn)n4為部分積輸入信號(hào);Cin為鄰近壓縮器進(jìn)位輸入;Sum為偽和;Carry和Cout為進(jìn)位輸出,其權(quán)值相同。由圖及表達(dá)式知, 輸出進(jìn)位與輸入進(jìn)位式相互獨(dú)立的,即輸出并不由輸入產(chǎn)生,這樣就能保證部分積同時(shí)且獨(dú)立地相加。4-2壓縮器對(duì)部分積進(jìn)行壓縮的圖如圖2【5】所示:

圖2 4-2壓縮器組結(jié)構(gòu)圖

由4-2壓縮器進(jìn)行部分積壓縮的Booth乘法器的Verilog HDL描述部分程序如下:

module Booth_radix_4(prod,ready,multiplicand,multiplier,start,clk);

……

dug dug0(PP0,mult[2:0]);

……

count count1(clock,sum0,carry0,PP0,PP1,PP2,PP3,cout0,cin0);

count count2(clock,sum1,carry1,PP4,PP5,PP6,PP7,cout1,cout0);

……

count count3(clock,sum,carry,sum0,carry0,sum1,carry1,cout,cin0);www.51kaifa.com

……

3.2 4-2和5-2混合壓縮器

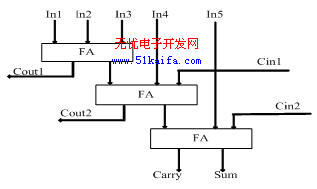

4-2壓縮器在很大程度上減少了部分積的求和速度,但是它有一個(gè)缺點(diǎn)是Sum(偽和信號(hào))比Carry(進(jìn)位信號(hào))的產(chǎn)生速度慢,因此,進(jìn)位信號(hào)必須等待偽和信號(hào)的產(chǎn)生,這樣又造成了壓縮速度的降低和功耗的增加.可以用異或門和2-1數(shù)據(jù)選擇器對(duì)電路進(jìn)行變換【6】,這種結(jié)構(gòu)能同時(shí)產(chǎn)生偽和信號(hào)和進(jìn)位信號(hào),并且關(guān)鍵路徑的延遲也只有全加器的1.5倍【8】。為進(jìn)一步壓縮部分積的求和級(jí)數(shù),加快壓縮速度,本文同時(shí)采用了4-2壓縮器和5-2壓縮器混合邏輯設(shè)計(jì)。5-2壓縮器的結(jié)構(gòu)圖如圖3【7】所示,

圖3 5-2壓縮器的結(jié)構(gòu)圖

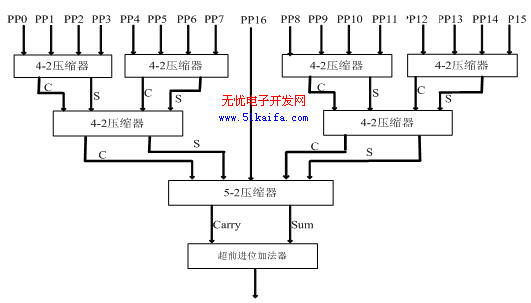

5-2 壓縮器有7個(gè)輸入In1~In5(權(quán)值相同),3個(gè)進(jìn)位輸出(權(quán)值相同)和一個(gè)偽和(權(quán)值比進(jìn)位輸出低一位),這種結(jié)構(gòu)的壓縮器結(jié)構(gòu)規(guī)整,且僅有6個(gè)異或 門的延遲。文獻(xiàn)[8]中給出了5-2壓縮器的輸入與輸出的邏輯關(guān)系表達(dá)式。整個(gè)壓縮器結(jié)構(gòu)圖如圖4所示:

圖4 本文采用的整個(gè)壓縮器結(jié)構(gòu)

由4-2和5-2混合壓縮器實(shí)現(xiàn)的改進(jìn)Booth乘法器的Verilog HDL描述部分程序如下:

module Booth_radix_5(prod,ready,multiplicand,multiplier,start,clk);

……

dug dug0(PP0,mult[2:0]);

dug dug1(PP1,mult[4:2]);

……

count count1(clock,sum0,carry0,PP0,PP1,PP2,PP3,cout0,cin0);

……

sum sum1(clock,sum,carry,In16,sum0,carry0,sum1,carry1,cout,cin0,cin1);

……

4邏輯仿真及性能比較

本文在Xilinx ISE和Quartus II兩種集成開發(fā)環(huán)境下, 對(duì)以上3種結(jié)構(gòu)的乘法器進(jìn)行了編譯、綜合、適配、時(shí)序仿真以及功率分析,其中輸入信號(hào)的字寬為32bit。有仿真工具Xilinx ISE和Quartus II進(jìn)行的仿真結(jié)果報(bào)告文件,很容易做出對(duì)這3種乘法器的性能比較,如表1所示。

表1 3種乘法器性能比較表

|

Resources Summary |

|||

|

乘法器類型 |

資源占用率 |

面積(mm2) |

時(shí)延(ns) |

|

兩位陣列乘法器 |

37/128(29%) |

6.91 |

8.285 |

|

4-2壓縮的Booth乘法器 |

38/256(15%) |

12.07 |

3.99 |

|

4-2和5-2混合壓縮的 Booth乘法器 |

35/256(14%) |

11.849 |

3.59 |

有性能比較表知:陣列乘法器面積最小,功耗小,但是運(yùn)行速度慢;單純使用4-2壓縮器的Booth乘法器在資源占用率和速度上要比陣列乘法器提高約1倍, 功耗略大于陣列乘法器;而本文設(shè)計(jì)采用的乘法器方案有效提高了乘法器的運(yùn)算能力,應(yīng)用在FPGA上工作頻率可達(dá)256.61MHz,要比傳統(tǒng)的4-2壓縮 器構(gòu)成的乘法器在速度上提高了10%,硬件資源占用減少了約1%。

4結(jié)論

不同架構(gòu)的乘法器在性能上都存在優(yōu)點(diǎn)和缺點(diǎn),在選擇乘法器時(shí),應(yīng)根據(jù)應(yīng)用場(chǎng)合的要求在速度、面積和功耗等方面綜合考慮,本文采用Xilinx ISE和Quartus II兩種集成開發(fā)環(huán)境對(duì)所實(shí)現(xiàn)的乘法器綜合進(jìn)行測(cè)試,更能準(zhǔn)確顯示不同結(jié)構(gòu)的乘法器的性能優(yōu)勢(shì),幫助用戶快速選擇合適的乘法器。本文設(shè)計(jì)采用的乘法器方案要比傳統(tǒng)的4-2壓縮器構(gòu)成的乘法器在速度上提高了10%,硬件資源占用減少了約1%,有效提高了乘法器的運(yùn)算能力。

本文作者創(chuàng)新點(diǎn): 本文采用4-2和5-2混合壓縮器對(duì)部分積進(jìn)行壓縮,減少了乘法器的延時(shí)和資源占用率;并用Verilog HDL語言實(shí)現(xiàn)了兩位陣列乘法器和傳統(tǒng)的Booth編碼乘法器。同時(shí)在Xilinx ISE和Quartus II兩種集成開發(fā)環(huán)境下進(jìn)行綜合仿真測(cè)試,這更有利于比較乘法器的性能優(yōu)勢(shì),便于用戶更準(zhǔn)確地選擇適合應(yīng)用場(chǎng)合的乘法器。

參考文獻(xiàn):

[1]王冠,黃熙,王鷹.Verilog HDL與數(shù)字電路設(shè)計(jì)[M].北京:機(jī)械工業(yè)出版社,2006

[2]Yijun Liu.An Asynchronous Pipelined 32×32-bit Iterative Multiplier Using Hybrid Handshaking Protocol.http://async.org.uk/ukasyncforum14/forum14-papers/forum14-liu. pdf

[3]何靜,李清峰.基于CPLD的混合邏輯乘法器的設(shè)計(jì)[J].微計(jì)算機(jī)信息,2006,22(17):244-246.www.51kaifa.com

[4]Dony C,Purchase J.Winder R.Exception Handling in Object-oriented System[C].Report on ECOOP91 Workshop W4,1991:17-30.

[5] 王新剛,樊曉椏,李瑛,等.一種并行乘法器的設(shè)計(jì)與實(shí)現(xiàn)[J].計(jì)算機(jī)應(yīng)用研究,2004,(7):135-137.

[6] Radhakrishnan D,Preethy A P. Low power CMOS pass logic 4-2 compressor for high-speed multiplications[c]∥Proceedings of the 43rd IEEE Midwest Symposium of Circuits and Systems. Piscataway,USA:IEEE,2000:1296

-1298.

[7] Pallavi Devi Gopineedi, Himanshu Thapliyal, M.B Srinivas, Hamid R. Arabnia. Novel and Efficient 4: 2 and 5: 2 Compressors with Minimum Number of Transistors Designed for Low-Power Operations,ESA,2006: 160-168.

[8]梁峰,邵志標(biāo),梁晉.Radix-16 Booth流水線乘法器的設(shè)計(jì)[J].西安交通大學(xué)學(xué)報(bào),2006,40(10):1111-1114.