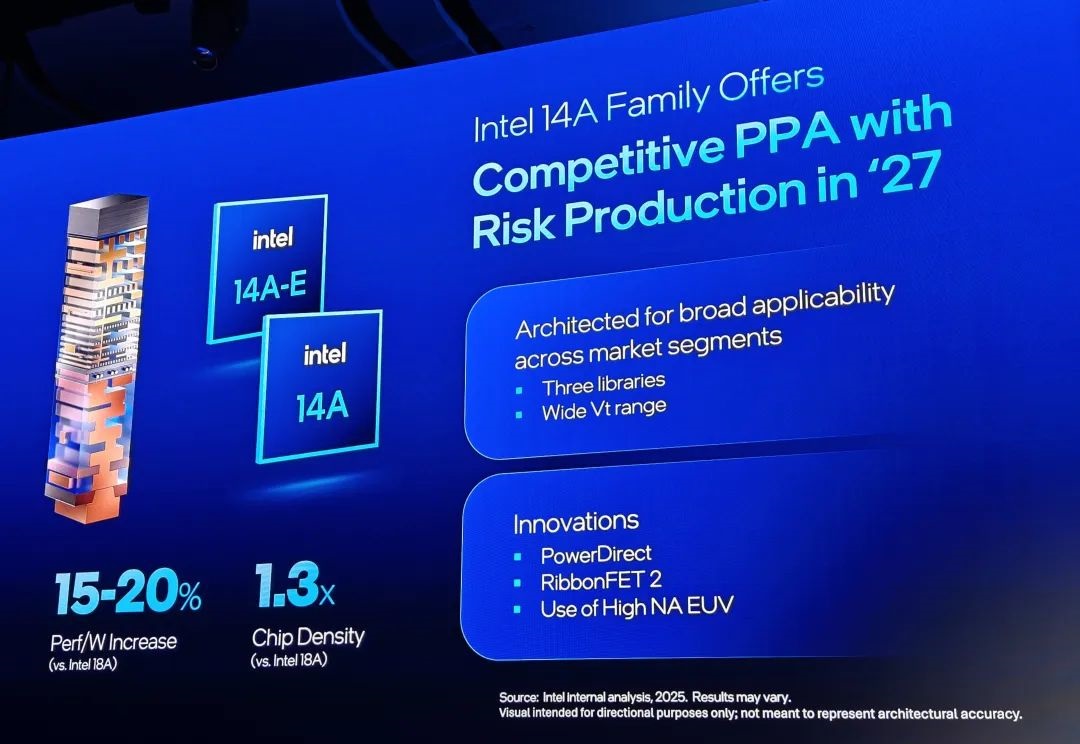

9月9日消息,據(jù)外媒Tom's hardware報(bào)道,英特爾首席財(cái)務(wù)官(CFO)David Zinsner在花旗 2025 年全球 TMT 大會(huì)上表示,下一代的Intel 14A(1.4nm級(jí))制程技術(shù)將是英特爾為代工客戶從頭開始設(shè)計(jì)第一個(gè)尖端制造工藝,因?yàn)槠鋵⑹褂肁SML最新的0.55NA(數(shù)值孔徑)的High NA EUV光刻機(jī)Twinscan EXE:5200B。

“14A 將比 18A 更貴,”David Zinsner坦言:“雖然就晶圓廠投資而言,14A并沒有明顯更貴。但這肯定會(huì)帶來更高的晶圓制造成本,部分原因是我們期望在 14A 中使用High NA EUV 工具,而 18A 中并非如此。”

英特爾預(yù)計(jì),與 18A 相比,其 14A 制造工藝的每瓦性能將提高 15% – 20%,功耗可降低 25% – 18%。14A還將采用第二代 RibbonFET 晶體管架構(gòu)(一種升級(jí)的柵極全方位晶體管結(jié)構(gòu))和全新的背面供電技術(shù) PowerDirect(一種將電源線直接連接到晶體管源極和漏極的背面供電網(wǎng)絡(luò))。

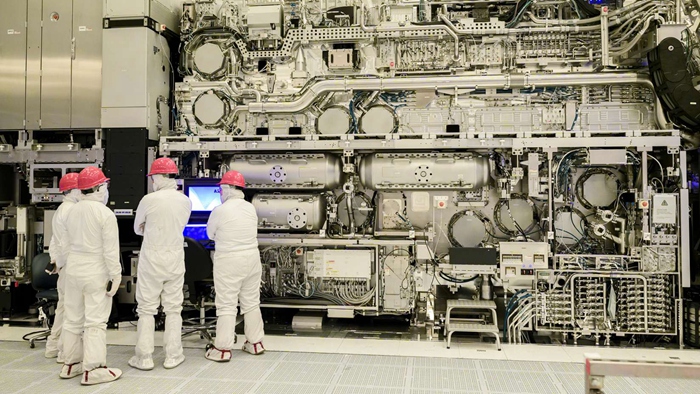

Intel 14A 還有一項(xiàng)關(guān)鍵創(chuàng)新是 Turbo Cells,它通過在密集的標(biāo)準(zhǔn)單元庫(kù)中使用高驅(qū)動(dòng)、雙高單元優(yōu)化關(guān)鍵時(shí)序路徑來增強(qiáng) CPU 和 GPU 頻率,從而在不影響面積或功耗的情況下提高性能。然而,為了實(shí)現(xiàn) 14A 生產(chǎn),英特爾需要使用High NA EUV 光刻系統(tǒng),這些系統(tǒng)可提供更好的分辨率,因此不需要依賴多圖案化。

ASML稱其High NA EUV 系統(tǒng)在單次曝光中實(shí)現(xiàn)了 8nm 分辨率,與當(dāng)前 Low-NA EUV 工具的 13.5nm 分辨率相比有著很大的提升。盡管 Low-NA EUV 系統(tǒng)也可以使用雙圖案化(雙重曝光)達(dá)到 8nm分辨率,但這種方法會(huì)增加工藝復(fù)雜度并影響良率。然而,High NA EUV將曝光場(chǎng)減少了50%,需要芯片制造商調(diào)整其設(shè)計(jì)策略。此外,High NA EUV比現(xiàn)有的EUV光刻機(jī)更昂貴。

ASML 當(dāng)前一代 Low-NA EUV Twinscan NXE:3800E 每臺(tái)成本約為 2.35 億美元,而High NA EUV Twinscan EXE:5200B(或更高級(jí))工具預(yù)計(jì)每臺(tái)成本為 3.8 億美元。由于該技術(shù)帶來的高成本和獨(dú)特挑戰(zhàn),各家晶圓廠對(duì)于何時(shí)采用High NA EUV的規(guī)劃各不相同:英特爾正在推動(dòng)幾年后利用High NA EUV量產(chǎn)14A,而臺(tái)積電則采取更謹(jǐn)慎的態(tài)度,其A16制程仍將采用Low-NA EUV。

旨在生產(chǎn)采尖端制程工藝芯片的晶圓廠目前的建設(shè)成本從 200 億美元到 300 億美元不等,具體取決于產(chǎn)能配置,因此以 15.2 億美元的價(jià)格增加四個(gè) High-NA EUV工具幾乎不會(huì)顯著增加晶圓廠成本。同時(shí),14A 研發(fā)成本高達(dá)數(shù)十億美元。因此,一旦所有額外成本都加上,它們確實(shí)會(huì)使 14A 工藝技術(shù)比 18A 更昂貴,這就是為什么英特爾代工需要外部客戶來證明額外成本的合理性。

“我認(rèn)為英特爾首席執(zhí)行官陳立武( Lip-Bu Tan)所說的是,如果我們沒有在外部獲得 14A 客戶,將很難證明該節(jié)點(diǎn)的合理性,”David Zinsner說。“所以,是的,英特爾產(chǎn)品將成為 14A 的大客戶,事實(shí)確實(shí)如此,我們需要確保它達(dá)到我們可以為股東帶來合理投資回報(bào)率的水平。”

此外,David Zinsner還確認(rèn),英特爾理論上可將晶圓制造業(yè)務(wù)最高49%股份出售給外部投資者,不會(huì)違反與美國(guó)政府協(xié)議。但是有興趣投資者有限,英特爾不太可能在未來幾年內(nèi)全面分拆晶圓制造業(yè)務(wù)并首次公開募股(IPO)。

不久前,美國(guó)政府以89億美元入股英特爾,獲得了英特爾約10%的股權(quán),根據(jù)協(xié)議,英特爾必須在5年內(nèi)保持對(duì)晶圓制造業(yè)務(wù)的控股權(quán)。若英特爾對(duì)晶圓制造業(yè)務(wù)持股低于51%,美國(guó)政府可再增持5%,顯示美政府對(duì)關(guān)鍵產(chǎn)業(yè)的控制權(quán)。