目前許多FPGA" title="FPGA">FPGA的邏輯資源(LE)都已超過1萬門,使得片上可編程系統SOPC" title="SOPC">SOPC已經成為可能。算術邏輯單元ALU" title="ALU">ALU應用廣泛,是片上可編程系統不可或缺的一部分。利用VHDL語言在FPGA芯片上設計ALU的研究較少,文中選用FPGA來設計32位算術邏輯單元ALU,通過VHDL語言實現ALU的功能。

1 電路總體設計思想

算術邏輯單元ALU采用模塊化設計,可以完成32位有符號數和無符號數的加減乘除,還可以實現9種邏輯運算、6種移位操作以及高低字節內容互換等操作。

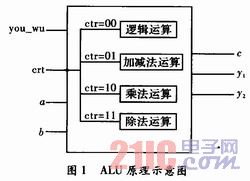

總體設計圖,如圖1所示。當you_wu=1時實現有符號數加減乘除運算,否則為無符號數運算。進行有符號數加減運算時c為符號位,無符號數加減運算時c表示進位或借位。加減法運算和邏輯運算結果存于y1。乘運算時,y1放高32位,y2放低32位。除法運算時y1放商,y2放余數。a,b表示兩路32位輸入數據。

2 主要模塊功能分析

算術邏輯單元ALU包含5個模塊:控制模塊、邏輯模塊、加減法模塊、乘法模塊和除法模塊。控制模塊比較簡單,即1個2線~4線譯碼器,完成其他模塊的控制與選擇。當ctr=00時完成邏輯運算,ctr=01時完成加減法運算,ctr=10時完成乘法運算,ctr=11時完成除法運算。

2.1 邏輯運算模塊

本模塊實現與、或、非、與非、或非、異或、同或、邏輯左移、邏輯右移、算術左移、算術右移、邏輯循環左移、邏輯循環右移以及高低半字(16位)分別取反和高低字內容互換等操作。用1個case語句即可實現上述全部功能。

2.2 加減法模塊

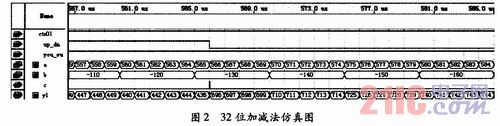

加減法模塊可根據需要完成32位有符號數和無符號數的加減運算,在程序開始時先判斷所要進行的運算有無符號數,對于有符號數,用符號位將兩組數擴展為33位二進制數,否則用0擴展為33位二進制數,其中減法運算采用補碼實現,所以整個程序只有加法運算。程序只占用68個邏輯資源(LE),非常節省資源,而且速度很快,是一種優化設計。仿真圖如圖2所示。

2.3 乘法模塊

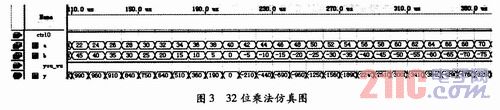

比較好的帶符號數的乘法是布斯(Booth)算法。但是本模塊既要實現有符號數運算,也要實現無符號數運算,用Booth算法反而復雜。綜合考慮邏輯資源的使用和速度兩個方面的因素,本設計采用下面的算法:不管是有符號數還是無符號數乘法,都轉換成無符號數相乘,最后根據需要對計算結果進行轉換。如果是無符號數相乘,乘積不作變化。如果是有符號數相乘,只有兩位乘數符號不一樣時才對乘的結果做處理,否則結果不變。乘積處理的方法是將乘積取反加1。假設乘數是32位數a,b,乘法主要通過移位和加法組成,設a=a31,a30…a0,如果ai=1則b向左移i位且右邊添i個0,否則b不作變化,a中有多少個1就要進行多少次移位操作,最后將所有移位值相加既得a×b的值。乘法的仿真圖如圖3所示。仿真結果表示設計完全正確。32位有符號和無符號數乘法模塊占用邏輯資源不到800 LE,且由于各種移位并發進行,故速度較快。

2.4 除法模塊

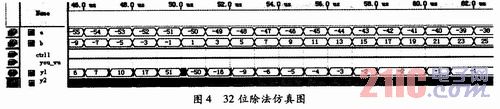

目前運用VHDL進行乘法運算的研究較多,而除法只有少數學者研究。文中綜合考慮速度和資源的占用,采取下列算法實現:對于32位無符號被除數a,先將a轉換成高32位是0低32位是a的數temp_a。在每個周期開始時temp_a向左移動一位,最后一位補0,然后判斷temp_a的高32位是否≥除數b,如是則temp_a的高32位減去b并且低32位加1,得到的新值仍賦給temp_a。如不是直接進入下一步。上面的移位、比較、減法要進行32次,經過32個周期后,運算結束,所得到的temp_a的高32位為余數,低32位為商。

對于32位有符號數的除法,采用的算法是將被除數與除數均變成無符號的32位數,緊接著的計算過程與無符號數除法一樣,只是需要判斷商和余數是正數還是負數。令![]() ,如果d=0則被除數與除數同為正數或者負數,最終商為正數。如果d=1說明被除數與除數符號相反,最終商為負數。被除數是負數時余數為負,否則為正。最后根據d的值對商作處理;如果d=0商不需任何處理,如果d=1則將商取反加1才是正確的結果。余數的調整則根據被除數的符號位進行。

,如果d=0則被除數與除數同為正數或者負數,最終商為正數。如果d=1說明被除數與除數符號相反,最終商為負數。被除數是負數時余數為負,否則為正。最后根據d的值對商作處理;如果d=0商不需任何處理,如果d=1則將商取反加1才是正確的結果。余數的調整則根據被除數的符號位進行。

3 結束語

文中在FPGA芯片上,利用VHDL語言設計了功能強大的32位ALU。由于ALU是CPU的重要組成部分,各類系統中都不可避免地需要ALU,因此本設計的應用泛圍較廣。