摘要:結合實際項目的開發經驗,詳細講解了基于Xilinx Microblaze軟核開發的整個流程,包括硬件平臺搭建、軟件平臺開發、嵌入式操作系統的加載以及用非易失性存儲設備對FPGA進行上電配置等內容。利用FPGA軟核進行嵌入式系統開發,將得到越來越多的關注和應用。

關鍵詞:嵌入式系統;軟核;片上可編程系統;可編程邏輯門陣列

引言

近十年來,FPGA行業獲得了突飛猛進的發展,其在系統開發工作中的地位已從簡單的膠合邏輯上升到了數字系統的核心處理器件。可編程片上系統SOPC(Systern On Programmable Chip)將CPU核與外設核以及系統軟件集成到單一芯片中,幫助用戶快速“量身定制”所需要的產品,創造性地為用戶提供了基于FPGA的嵌入式設計方案。

Xilinx公司作為FPGA嵌入式軟核解決方案商,在其所有系列的FPGA中提供了Microblaze 32位軟核處理器,并推出了用于嵌入式系統編程的EDK(Embedded Development Kit)集成開發解決方案。本文結合實際項目的開發經驗,詳細講解了基于Microblaze軟核開發的整個流程,包括硬件平臺開發、軟件平臺開發、嵌入式操作系統的加載以及用非易失性存儲設備對FPGA進行上電配置等內容。

1 Microblaze的體系結構

Microblaze處理器采用RISC架構和哈佛結構,在時鐘頻率為150 MHz的情況下可以達到125 DMIPS的性能,該處理器(版本7.30)具有以下一些特征:

①32個32位通用寄存器和最多18個專用寄存器;

②32位指令系統,支持3個操作數和2種尋址方式;

③分離的32位指令和數據總線;

④通過本地存儲器總線LMB直接訪問片內的塊存儲器BRAM;

⑤具有高速的指令和數據緩存Cache,5級流水線結構;

⑥自帶硬件調試模塊MIDM;

⑦帶有8個主/從快速單工鏈路接口。

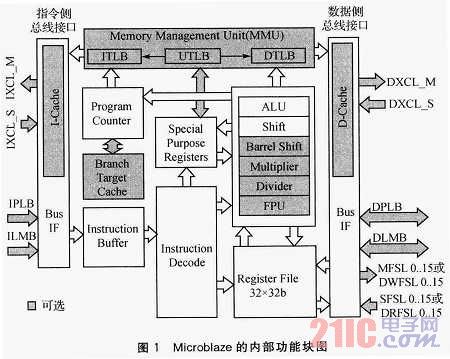

圖1給出了Microblaze的內部功能塊圖。

從圖1可以看出,Microblaze軟核與其他專用集成芯片的硬CPU核在結構上沒有大的差別,但它卻可以通過PLB總線(Processor Local Bus )與EDK軟件包將自帶的各種軟外設進行按需連接,并且支持用戶自定義IP通過PLB總線(Microblaze從7.30版本開始取消了原有的OPB總線)和FSL(Fast Simple Link)總線與Microblaze軟核連接,從而最大限度地發揮FPGA設計的靈活性。

2 基于Microblaze的嵌入式開發流程

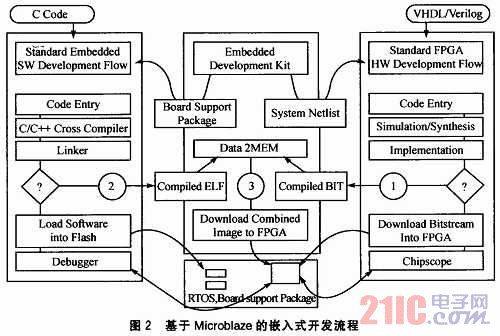

如圖2所示,基于Microblaze的嵌入式開發流程主要包括3個步驟:首先要搭建起底層的物理平臺,包括構建Microblaze處理器,將所需的外設通過片內總線掛到Microblaze處理器上,并根據需要開發用戶自定義的IP核;第二步在構建起的硬件平臺上編寫軟件應用程序,包括應用程序代碼、庫文件以及板級支持包BSP等;最后將硬件的比特流配置文件和軟件的可執行重定位文件進行合并形成最終的文件,或者直接下載到FPGA內部運行,或者下載到FPGA片外的非易失性存儲器Flash中,在系統配置完成后由Bootloader。程序將Flash中的應用程序拷貝到片外的DDRRAM中運行。

2.1 硬件平臺的開發

EDK的組件XPS(Xilinx Platform Studio)為Microblaze提供了一個集成開發環境,硬件平臺的開發主要包括兩方面內容:

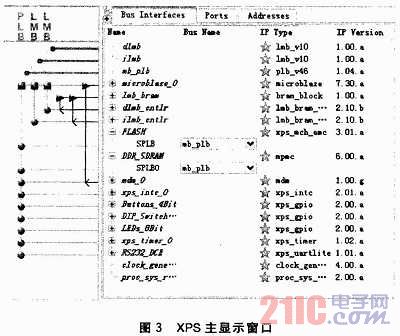

①用基本系統向導BSB(Base System Builder)搭建Microblaze平臺,包括FPGA器件型號的選擇、Microblaze處理器屬性的設置、所需外設的添加和屬性設置、測試程序的生成等步驟。圖3給出了BSB完成后的XPS顯示窗口內容。從圖3可以看到,系統添加了多種外設,如RS232串口、與外部Flash和。DDR RAM進行交互的控制邏輯、中斷控制器和定時器等,這些外設通過指定的片內總線連接到Microblaze控制核上。除此之外,還可以在Ports頁面對各個模塊的信號進行相互連接,在Addresses頁面對模塊的地址進行分配等。這部分工作相當于將原本不可分割的ASIC專用集成芯片進行了拆卸,讓用戶深入到芯片內部,根據自身的需求去選取芯片需要具備的功能模塊,并完成這些模塊與控制核的連接和地址分配,形成用戶最終定制的底層邏輯。這種拆卸和組合在一定程度上增加了系統開發的難度,但也換來了系統設計的靈活性、通用性和可擴展性。

②定制用戶自己的IP核。由于嵌入式系統開發的特殊性,有時可能很難找到一款ASIC控制器,具備系統要求的所有外設接口。在這種情況下,要么用軟件實現所缺的外設功能,從而犧牲了系統性能;要么單獨購置一片該接口芯片,從而增大了電路板面積和成本。而基于FPGA軟核的設計則不存在這種問題。在XPS中定制用戶IP核與一般用VHDL編寫邏輯電路不同的是,這種定制IP可以掛接在PLB總線上,從而實現與Microblaze的通信。XPS提供自定義IP核的生成向導,圖4給出了用戶自定義IP核的邏輯結構。從圖可以看出,生成向導創建了兩個模塊,一個是與PLB總線進行交互的接口模塊IPIF,另一個是用戶邏輯模塊User_Logic。IPIF完成PLB總線信號的捕捉和協議轉換,這部分內容不需要用戶參與,用戶只需根據自定義邏輯的輸入/輸出信號在IPIF中給出相應的聲明即可;User_Logic模塊則是需要用戶進行手動添加自定義邏輯代碼的地方,在這里用戶只需關注自己需要實現的功能,不用擔心它們與Microblaze之間的通信鏈接。

2.2 軟件平臺的開發

EDK的另一個組件SDK是對于XPS集成開發環境的補充,提供了一個軟件工程項目的開發環境,具有以下功能和特點:

◆基于Eclipse開源代碼標準;

◆項目管理;

◆功能完善的C/C++代碼編輯和編譯環境;

◆程序創建配置和自動化的Makefile生成;

◆完美集成的對嵌入式對象的無縫調試環境。

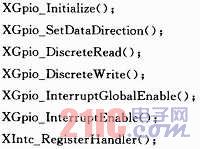

除了提供軟件的開發環境外,Xilinx公司還提供了各種IP核的API控制函數,這些API被安放在..\EDK\SW\XilinxProcessorIPLib\drivers目錄下,其中..\表示Xilinx軟件的安裝目錄。通過閱讀IP核的PDF說明文檔和API函數的C代碼,用戶可以很容易地實現對IP核的控制。以通用輸入/輸出端口GPIO為例,在文件夾..\EDK\sw\XilinxProcessorIPLib\drivers\gpio_v2_13_a下存放著與GPIO軟件編程有關的所有內容,其src子目錄下包含各種API函數的C源碼,doc目錄下包含對各種API函數的使用說明,而examples目錄下還有針對GPIO進行編程的實例源碼。一般對GPIO的操作過程為:

即首先對GPIO口進行初始化,然后設置其方向為輸入或是輸出,接下來就可以對GPIO進行讀寫。如果該GPIO可以產生中斷,則必須置位其中斷使能位,然后將中斷處理函數掛接到中斷控制器或直接掛到Microblaze的中斷位上。

2.3 Chipscope調試

Chipscope是Xilinx公司的片內調試工具,通過將邏輯分析器、總線分析器和虛擬I/O小型軟核插入到用戶的設計當中,可以查看和分析任何內部FPGA信號,包括嵌入式處理器總線。信號被實時采集,并從編程接口JTAG傳輸到主機,然后通過Chipscope Pro邏輯分析器進行分析。Chipscope的典型工作模式支持4種Chipscope Core,它們具有不同的功能和適應環境:

①Chipscope_icon,用于管理其他的Chipscope core,所有的Chipscope core都是通過這個核連接到FPGA的JTAG口;

②Chipscope_ila,用于監控FPGA內部的自定義信號,是使用范圍最廣的監控核;

③Chipscope_plb46_iba,用于監控PLB總線;

④Chipscope_vio,用于監控FPGA內部的實時自定義信號變化。

Chipscope使用的幾個主要步驟包括:

①調用Chipscope Pro Core Generator,生成需要使用的Chipscope cote,并加入到工程中;

②調用Chipseope Pro Core Inserter,選擇需要監控的信號,設置采樣和匹配參數,并將配置后的Chipscopecore插入到設計中;

③調用Chipscope Pro Configuration,包括ChipscopePro On-Chip Debugging和Chipscope Pro On-Chip Verification,即通過Chips-cope的分析器工具Analyzer觀察FPGA內部信號,并和設計者的需求進行比較,分析不一致的時序。

3 為系統添加嵌入式操作系統

如果系統所涉及的功能比較復雜,或者系統對實時性要求比較嚴格的話,在自己的設計中加載一個嵌入式操作系統是一個很好的選擇。Xilinx FPGA目前支持絕大多數主流嵌入式操作系統,如VxWorks、Embedded Linux、μClinux、μC/OS-II和PetaLogix等,而μC/OS-II因其具有移植方便、執行效率高、占用空間小、實時性強和可靠性高等優點,成為Microblaze軟核的首選嵌入式操作系統。μC/OS-II的大部分源代碼是用ANSI C語言編寫的,它的移植只需改寫與處理器有關的3個文件即可。

如圖5所示,修改與處理器相關的常數和宏定義頭文件OS_CPU.H、任務切換過程中的堆棧處理匯編文件OS_CPU_A.ASM和鉤函數定義文件OS_CPU_C.C。最簡便的做法是在μC/OS-II官方網站www.micrium.com上下載an1013.zip壓縮包,里面包含針對Microblaze修改好的3個移植文件、μC/OS-II軟件代碼和μC/OS-II應用指導文檔,根據文檔的描述將壓縮包中的相關文件放到Xilinx的指定安裝目錄下,就可以在S-DK中直接選用μC/OS-II操作系統。此外,壓縮包中還提供了一個示例程序,用于演示μC/OS-II操作系統是否在Microblaze系統上運行正常,極大減輕了用戶在移植μC/OS-II過程中所面臨的工作量。

4 FPGA的配置

基于SRAM結構的FPGA每次上電都需要外部的配置芯片對其進行加載,Xilinx的FPGA提供了多種配置方式,如簡便的Platform Flash PROM主串配置、價格低廉的SPI配置、大容量的并行配置和JTAG配置等,用戶可以根據自己的實際情況進行靈活選擇。結合iMPACT圖形化配置軟件,向片外配置芯片燒寫比特流的工作變得非常簡單,極大縮短了系統的開發時間。除了常規的配置方式外,Xilinx FPGA還支持將多個配置文件放在一個配置芯片中實現系統的多配置啟動,或者將用戶數據存放在配置芯片中,在系統配置完成后根據需要隨時從配置芯片中讀出用戶數據。在Xilinx的官方網站www.xinlinx.com上可以下載關于芯片配置的各種應用文檔,使用戶在嵌入式系統開發過程中最大限度地發揮FPGA的靈活性。

結語

基于FPGA軟核的嵌入式系統開發分為硬件平臺開發和軟件平臺開發兩個部分,在硬件平臺開發過程中可以根據需求選擇外設,也可以定制自己的IP,實現更為靈活的接口和控制功能;在軟件平臺開發階段則可以充分利用XPS提供的API制函數,方便快捷地編寫控制程序。FP-GA進行嵌入式系統開發所具備的定制性正受到越來越多的青睞和關注,可以預見,未來使用FPGA進行嵌入式產品的開發必將成為潮流。