超高速快速傅里葉變換(FFT)內核是任何實時頻譜監測系統的必要組成部分。隨著各頻段無線設備數量的迅速增長,系統必須相應加強對帶寬的監測。因此,這些系統需要以更快的速度將時域轉換為頻域,這就要求進行更加快速的FFT運算。實際上,大多數現代監測系統往往需要使用并行FFT,實現數倍于尖端FPGA(例如賽靈思Virtex®-7)最高時鐘頻率的采樣吞吐量,充分發揮寬帶A/D轉換器的優勢,其可輕松獲得12.5Gsps甚至更高的采樣率。[1]

同時,隨著通信協議日益數據包化,監測信號的占空比在不斷降低。這種情況要求大幅度降低掃描重復時間,這就需要使用低時延FFT內核。并行FFT也能在這方面有所裨益,因為時延會隨著采樣率與時鐘速度之比成比例下降。

鑒于所有這些原因,本文將深入介紹可在運行中配置轉換長度的并行FFT(PFFT)設計,并說明使用并行FFT可實現的吞吐量和利用率。

FFT的硬件并行化

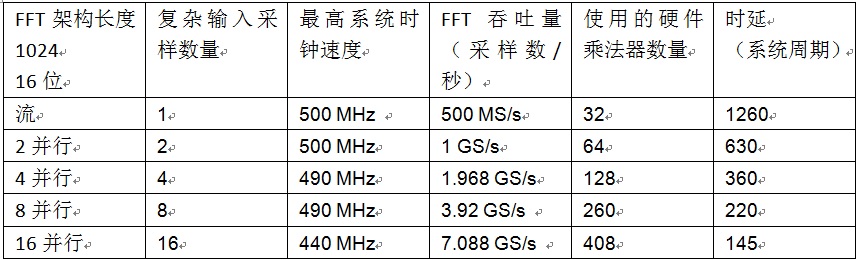

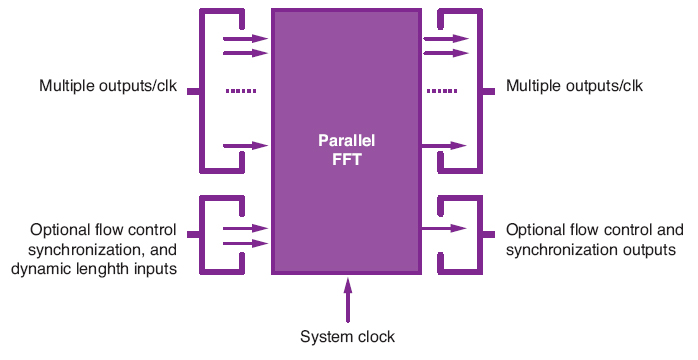

由于在邏輯中直接實現FFT較為復雜,因此大量硬件設計人員使用各個廠商提供的現成FFT內核。[2]但是,大多數現成的FFT內核使用“流”或者“模塊”架構,每個時鐘周期只能處理一個或者幾個采樣,這就會把吞吐量限制在FPGA或者ASIC器件所能提供的最大時鐘速度內。PFFT能夠提供速度更快的架構。PFFT每個時鐘周期可接受多個采樣,進行并行處理,并在每個時鐘周期內輸出多個采樣。這種架構可讓吞吐量達到器件最大時鐘速度的數倍,但代價是增大了占位面積并提高了復雜性。因此,要使用PFFT必須在吞吐量和面積之間進行權衡。典型Virtex-7 FPGA設計所需的權衡方案見圖1和表1。

在Virtex-7器件上實現并行FFT的典型性能和面積權衡

表1 - 面積的增加因硬件乘法器的使用造成。吞吐量提升與占位面積之比略高于線性關系,總體而言非常適用于將吞吐量增加至數千兆赫茲采樣率。

從權衡的角度,可從表中看出一些普遍特點:

1. 隨著并行吞吐量的增加,乘法器(面積)的使用也在增加,但增加的速度稍低(好于線性關系)。

2. 隨著并行量的增加,系統時鐘速度和時序收斂速度的下降會導致吞吐量的提升低于線性關系。不過在現代FPGA上這種劣化現象正在減輕。

3. 鑒于上述兩個原因,吞吐量增長與面積增長的比率總體上要高于線性關系。

4. 時延隨著并行化的增大而降低。

請注意表1中的測量值只適用于特定的對象和FFT配置。這種情況針對的是長度為1024的情況,且具有16位輸入、動態長度可編程(最小可編程長度為4)和流控制。流控制對頻譜監測這樣的應用而言非常重要,因為,這類應用往往需要在進行采集等其它操作時,使用旁通道信息來改變FFT大小(以改變分辨帶寬)或暫停FFT的運行。從理論上說,您可以通過在轉換操作前插入緩存的方式來實現流控制。但是對于頻譜監測這樣的采集驅動型操作而言,難以提前計算出所需要的緩存大小,這樣就必須采用容量大、速度快的高成本內存條。

實現架構

雖然實現FFT的方法多種多樣,但并行版本的Radix2多路徑延遲換向器內核(Radix2-MDC)[3] 作為一個模塊化方案在這里非常適用,可用于創建在先進FPGA器件中具有良好擴展能力的可配置并行FFT內核。Radix2-MDC是一種用于創建各種長度流水線FFT的典型方法,圖2a是長度為16的FFT。它將輸入序列分解為兩個并行數據流,并在數據流向前流入蝴蝶算法單元(FFT算法的一個子元)的過程中采用恰當的延遲對數據元進行調度,以確保數據元之間保持恰當的“間距”。如圖2b所示,使用較寬的數據路徑和矢量運算,Radix2-MDC的并行化就會相對容易。MDC的結構還便于實現流控制和動態長度重配置,相反,單路徑延遲反饋(SDF)結構因為加入了流控制(停止)信號,會顯著降低最大吞吐量。

圖1 - 并行FFT一次可處理多個采樣,使吞吐量超過目標器件可實現的系統時鐘速率。可選特性包括流控制、同步和動態長度可編程功能。

另一個會影響可擴展性的因素是復雜乘法器的選擇,即選擇4乘(4M)還是3乘(3M)結構。選擇3M復雜乘法器可以減少設計的占位面積,但代價是會降低時鐘速度。[4]這方面的權衡也主要依賴于FPGA器件的DSP硬件部分。下面是我們即將介紹的案例研究所使用的最重要的參數和選擇:

l 長度=1024

l 輸入精度=16位

l 使用4乘5加復雜乘法器的Radix2-MDC架構

l 數據路徑精度=每級增加1位(對1024長度為10級/位)

l 包含動態長度可編程功能

l 啟用可選的流程控制和同步功能