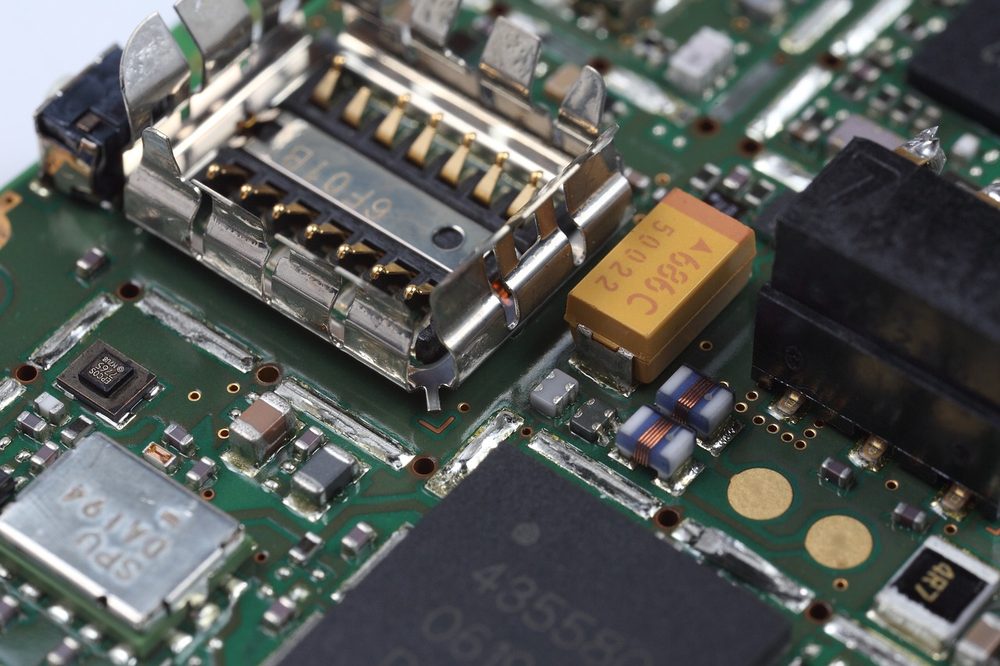

在高速電路設計中,PCB(印刷電路板)的層疊結構設計是至關重要的一環。合理的層疊結構不僅能夠保證信號的完整性,還能提高電路板的整體性能和可靠性。本文將詳細探討PCB多層板打樣中的層疊結構設計。

一、層疊結構的基本組成

PCB層疊結構主要由Core和Prepreg(半固態片,簡稱PP)組成。Core具有兩個表層銅箔,表層之間填充的是固態材料;而PP則起填充作用,材質為半固態樹脂。不同的Core和PP厚度選擇可以構成多樣化的層疊結構,以適應不同的設計需求。

二、層疊結構設計的先決條件

在進行層疊結構設計之前,需要明確以下幾個先決條件:

單板總層數:根據單板尺寸、信號數目、電源種類以及EMC(電磁兼容性)要求,確定信號層、電源層、地層的數目,從而得到單板的總層數。

單板厚度:通常,14層以內的單板厚度可選為1.6mm,而16層以上的單板厚度則需達到2mm以上。

目標阻抗:從信號完整性角度考慮,單端信號對地阻抗一般取50Ω,差分對信號間阻抗取100Ω。

PCB材質:主要關注介電常數(Er)和材質正切值(tanδ)。Er影響高頻信號的導通能力,而tanδ則決定信號的損耗。在高速電路設計中,應盡量選擇Er和tanδ較小的材質,但這也相應地增加了PCB的成本。

三、層疊結構的設計流程

層疊結構設計的目標是確定信號層、電源層、地層的排列順序,以及各層的厚度和信號線上的參數。具體流程如下:

評估信號層數目:根據布局設計和關鍵器件間的信號線密度,評估所需信號層的數目。

評估電源層和地層數目:根據電源種類和信號層隔離要求,確定所需電源層和地層的數目。

選擇材質:根據目標阻抗和信號完整性要求,選擇合適的PCB材質。

設計層疊結構:結合先決條件,設計信號層、電源層、地層的排列順序和各層厚度。

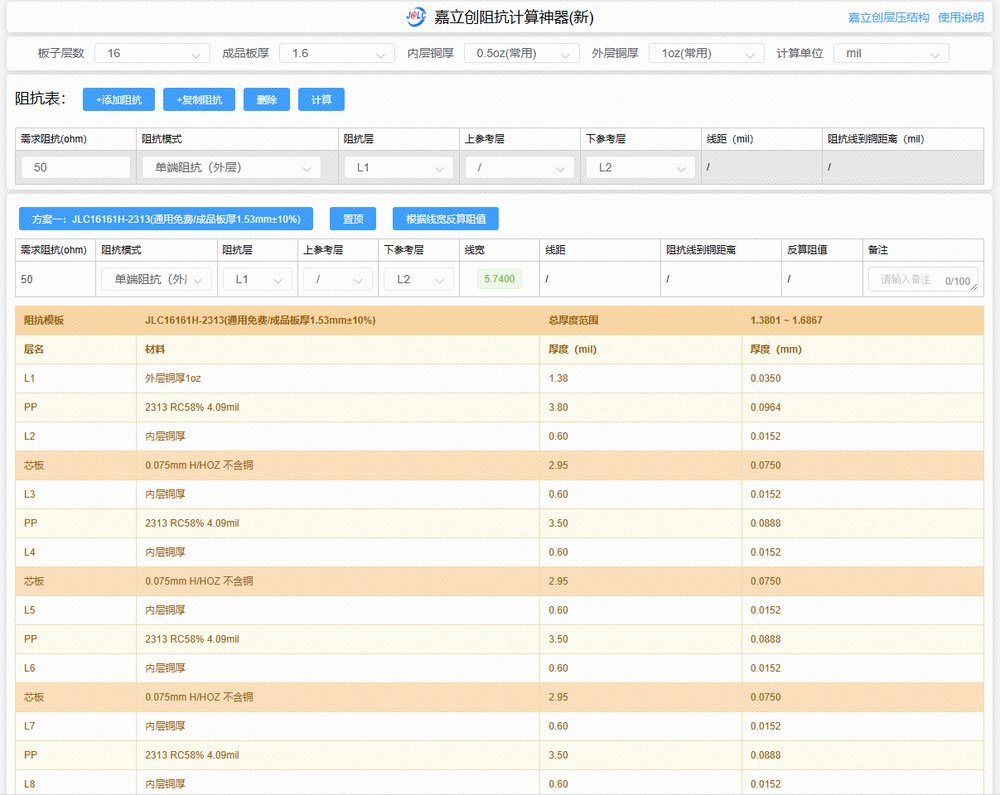

計算線寬和層厚:利用阻抗計算工具,根據目標阻抗和層疊結構參數,計算信號線的線寬和層厚。信號的阻抗可利用Polar Instruments公司開發的Polar SI6000或者嘉立創的阻抗計算神器等工具計算。

四、層疊結構設計的案例分析

以一個16層PCB為例,該板包含10層信號層、3層電源層和3層地層。在設計過程中,需要注意以下幾點:電源平面與地平面的緊密耦合:這有助于降低阻抗,提高信號完整性。關鍵信號線的走線層選擇:高速關鍵信號應走在信號完整性最好的層上,如以完整地層為參考的信號層。線寬與層厚的匹配:為獲得特定的目標阻抗,信號線寬需與信號所在層距離其相鄰參考層的間距相匹配。表層的使用:表層主要用作BGA器件或貼片器件的信號線扇出,不用于長距離走線。

五、高速電路中的特殊考慮

在高速電路設計中,還需特別關注以下幾點:

阻抗控制:確保信號層與其參考層之間盡量以固態材料填充,以獲得更好的阻抗控制效果。

正交走線:相鄰平面在走線時,應采用正交走線方式,以減少信號干擾。

電源層和地層的分割:分割的電源層與地層需保持良好的耦合,以減少電磁干擾。

六、結論

PCB多層板的層疊結構設計是高速電路設計中的重要環節。通過合理的層疊結構設計,可以確保信號的完整性,提高電路板的整體性能和可靠性。在實際設計中,需要綜合考慮單板總層數、單板厚度、目標阻抗和PCB材質等因素,并結合具體案例進行分析和優化。同時,還需特別關注高速電路中的特殊考慮,如阻抗控制、正交走線和電源層/地層的分割等。通過科學的層疊結構設計,可以為高速電路的穩定運行提供有力保障。