首次流片成功取決于整個系統(tǒng)硬件和相關軟件的驗證,有些公司提供的快速原型生成平臺具有許多調試功能,但這些平臺的價格非常高,因此最流行的做法是根據(jù)DUT和具體應用設計復合FPGA板,驗證這些板的原理圖通常是很麻煩的,本文提出一種利用FPGA實現(xiàn)原型板原理圖驗證的新方法。

|

|

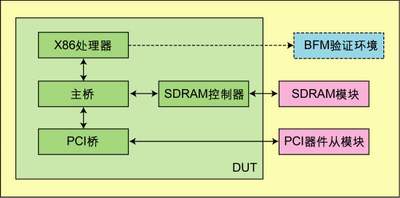

圖1:DUT由x86處理器、主橋(Host Bridge)、 |

由 于價格競爭越來越激烈,首次流片成功或只需少量的修改變得越來越重要。為了達到這一目標,對整個系統(tǒng)(即硬件和相關軟件)的驗證成為重中之重。業(yè)界也涌現(xiàn) 了許多策略來幫助設計師完成RTL上的軟件運行。這些策略提供了在最終硬件還在醞釀之時就開發(fā)軟件的一種途徑。這種措施也許還不夠,原因還有兩個:一是仿真系 統(tǒng)可能與實際系統(tǒng)有較大的區(qū)別,二是系統(tǒng)運行速度非常慢。因此可以考慮先將完整的設計映射到FPGA中,再運行目標應用程序。這樣做可能達不到最終硅片的 常規(guī)指標,但可以測試整個硬件的功能,系統(tǒng)能夠得到全面的驗證,其中一些測試案例可能是在仿真中根本無法完成的。另外,可用于演示的完整系統(tǒng)原型在硅片成 功之前就可以很好地引起客戶的興趣。

有些公司提供的快速原型生成平臺具有許多調試功能。這些電路板平臺具有可編程的互連,可以將FPGA插接在上面,并將DUT(被測設計)映射進這些FPGA中。但這些平臺的價格非常高。因此最流行的做法還是根據(jù)DUT和具體應用設計復合FPGA板。當然,這些板同樣也能用于測試目標應用中的最終硅片。

驗 證這些板的原理圖通常是很麻煩的,因為原理圖中一些小錯誤會嚴重影響到設計進度。原理圖驗證工作是人工完成的,因此錯誤也就在所難免。如果能夠復用DUT 驗證環(huán)境驗證電路板原理圖,那么原理圖驗證就可以派上用場了。本文將討論如何通過編寫少量腳本和修改DUT驗證環(huán)境達到這一目的。

方法簡介

基 本想法是設法對原理圖進行仿真。這了做到這一點,先將原理圖網(wǎng)表轉換成Verilog網(wǎng)表。電路板上安裝的不同元件(如FPGA、處理器、PCI卡、 SDRAM等)要么用RTL代替,要么用RTL驗證過程中使用的行為模型替代。值得注意的是,我們已假設整個設計的Verilog/VHDL代碼是現(xiàn)成 的。至于電路板上需要用于測試DUT的處理器、SDRAM、PCI器件等其它元件,也假設已經(jīng)存在相應的BFM(總線功能模型)/模型。由于這一階段是在 功能驗證之后,而這些元件需要用來測試DUT,并模擬整個系統(tǒng),因此它們的等效行為模型應該在功能驗證中已經(jīng)得到使用,現(xiàn)在只是重復使用罷了,即經(jīng)過少許 的努力就能使用相同的環(huán)境和測試案例。

上述概念經(jīng)過拓展就可以驗證硅片生成板的原理圖,基本的假設是設計團隊擁有硅片的 HDL描述。這才是要點所在。對于FPGA板,可以通過某種變通的方法配置FPGA引腳來克服由于原理圖中的錯誤連接導致的問題,即設計師可以管理并解決 這些錯誤。但對于準備用來測試最終硅片的板子來說幾乎是不可能的。

生成Verilog網(wǎng)表

|

|

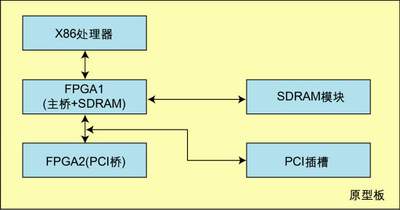

圖2:包含x86處理器芯片、2個FPGA、 |

可以用好幾種原理圖輸入工具生成Verilog網(wǎng)表。基于以下幾種限制原因,這種網(wǎng)表實際上是不能使用的:

1.它將板上的每個元件都看作是一個模塊,因此生成的Verilog文件中包含所有元件的實例,如FPGA、電容、上拉電阻或晶振,而不管這些元件能否在Verilog中建模。其中有些元件(如串接電阻、去耦電容)可以簡單地從網(wǎng)表中刪除。

2. 原理圖中的總線通常被連接到符號上的一個個引腳,而在Verilog模塊中總線可能只有一個端口。因此可能沒有一對一的對應關系。例如在Verilog模 塊中一個四位輸出地址總線將被聲明為:output [3:0] Address;但原理圖中所有這四個引腳是被獨立聲明的。這樣會導致原理圖中使用的符號的引腳輸出與Verilog模塊中相應符號的可用功能不兼容。

因此,設計師需要編寫一個簡單的腳本,要么修改這個Verilog網(wǎng)表,要么根據(jù)原理圖輸入工具支持的其它格式創(chuàng)建一個新的網(wǎng)表。目的是刪除電阻、電容、電感等模擬元件,或用等效的Verilog代碼替換它們。

為了更好地實現(xiàn)這一目的,可以利用對模擬元件的命名慣例,或將它們定義在一個文件中作為腳本的輸入。例如,電阻可以被命名為R1、R23等,不遵循這個命名慣例的元件可以被定義在約束文件中,這樣腳本就可以將它們關聯(lián)到等效模型,或假定短路將它們從網(wǎng)表中去除。

一般來說,針對電路板上的不同元件可以采用以下一些慣例:

1. 元件的大多數(shù)電源引腳可以被忽略。

2. 通常電容都是用作去耦的,可以被簡單的忽略掉,因為這樣做并不會影響即將被仿真的其它數(shù)字元件之間的互連關系。

3. 電感也可以忽略,在仿真時用短路代替。

4. 電阻可以用Verilog的上拉/下拉或簡單的線按需要替換。

5. 晶振可以用Verilog庫中提供的時鐘模塊替換。

可以在約束文件中定義某些特殊情況,并作為腳本的輸入。可以為Verilog模塊編寫Wrappers以克服總線聲明問題。這種頂層Verilog網(wǎng)表可以代替DUT功能驗證中早已使用的頂層Verilog文件,并用于驗證環(huán)境中。

FPGA原型板網(wǎng)表的仿真

至此頂層Verilog文件中包含了原型板上除工具刪除的元件外的所有元件。設計師可以復用DUT功能驗證使用的已有仿真環(huán)境。這種方法的優(yōu)點在于,可以復用相同的測試向量和驗證環(huán)境驗證原理圖。

任 何驗證環(huán)境的基本原理都是一樣的,即為DUT提供某種形式的測試向量,然后對測試結果與期望值進行比較。根據(jù)設計的復雜性有多種達成的方式。通過下面這個 非常簡單的例子就很好理解了。例子是一個基于x86處理器的SOC。為了簡單起見,我們只考慮圖1所示SOC中的少量重要元件。DUT由x86處理器、主 橋(Host Bridge)、SDRAM控制器和PCI橋組成。在驗證環(huán)境中,為了提高仿真速度,可以把x86處理器看作是一個BFM,同時提供某種PCI從模型。簡 單地說,x86 BFM具有某種形式的讀/寫命令,能產生總線周期,因此設計可以運行起來。

|

|

圖3:Verilog模塊創(chuàng)建wrapper |

如 圖2所示,主橋和SDRAM控制器被映射進FPGA1,PCI橋被映射時FPGA2。由腳本產生的頂層Verilog文件包含如圖2所示的所有元件。至此 就可以在驗證環(huán)境中方便地使用這個頂層Verilog文件,并附于相同的驗證測試向量。要注意的是還需要為各個Verilog模塊創(chuàng)建wrapper以匹 配元件的引腳。對于SDRAM和PCI槽道來說,可以使用與RTL驗證環(huán)境中使用的相同模型(即SDRAM模型和PCI主/從模型)。參考圖3,將 FPGA1作為案例進行說明。

由于只對環(huán)境作了少量修改,如在編譯列表中增加很少的Verilog文件(wrapper模 型),用新創(chuàng)建的文件替換頂層文件,因此可以對原理圖列表實施驗證。這些事情可以通過簡單的perl或shell腳本實現(xiàn)自動處理,整個任務將減少到僅指 定一些特殊選項,同時從命令行運行仿真。

如果有任何錯誤的連接,或某些連接被遺忘,那么仿真結果就會有相應的提示。這種方法可以實現(xiàn)對與模擬元件的連接的部分測試,因為這部分元件有的從網(wǎng)表中刪除了,有的被等效行為模型所代替。然而,有些錯誤還是可以被檢出的。

硅片生成板網(wǎng)表的仿真

上 述方法同樣可以用來仿真設計用于測試最終硅片的電路板的網(wǎng)表。這種方法更適用于對這些板的驗證,因為正常情況下制造出來的許多板其芯片的并行測試都是可以 完成的。此外,通過某種途徑配置FPGA引腳可以消除基于FPGA的板上的錯誤。下面繼續(xù)以上文的例子說明如何將同一概念應用到硅片生成板上。

如 圖1所示,硅片等效于DUT。根據(jù)相同的流程創(chuàng)建一個Verilog網(wǎng)表,這個網(wǎng)表將DUT看作是板上的一個芯片和其它外圍設備。這是在驗證環(huán)境中必須使 用的頂層文件。現(xiàn)在我們已經(jīng)有了DUT的完整Verilog描述,因此只需要創(chuàng)建圖4所示的Verilog wrapper,讓引腳輸出與電路板上的芯片相匹配。

綜上所述,這個網(wǎng)表是可以利用以前使用的同一測試向量進行操作的。

本文小結

這 種方法已經(jīng)過測試,目前正用于原理圖的驗證。該方法為原理圖驗證增加了新的方案。原型/生成板的原理圖的驗證和錯誤檢測可以在極易產生嚴重問題并影響設計 周期的早期階段進行。另外,驗證無需額外的開銷,因為這種方法基于的是業(yè)界常說的‘復用’原理,在本案例中復用的是測試向量和驗證環(huán)境。

|

|

圖4:Verilog wrapper讓引腳輸出 |

參考文獻:

* Protel98 - Designers Handbook, Protel.

* Thomas & Moorby's, The Verilog Hardware Description Language, Third Edition, Kluwer Academic Publishers.

* Ellie Quigley, PERL by Example, Pentice Hall PTR.

* John R. Levine et al, Lex & Yacc: O'Reilly & Associates, 2nd edition October 1992.

* Brian W. Kernighan, Dennis M. Ritchie, The C Programming Language, Second Edition, Prentice Hall Of India Pvt Ltd.

* OrCAD Capture 7.20 Design Tutorial, OrCAD.

術語

DUT-被測設計

BFM-總線功能模型

RTL-寄存器轉移級

SOC-系統(tǒng)級芯片

HDL-硬件描述語言

FPGA-現(xiàn)場可編程門陣列

PCI-外圍設備互連

作者:Kapil Batra

高級工程師

STMicroelectronics Pvt. Ltd.

Mahesh Chandra

項目經(jīng)理

STMicroelectronics Pvt. Ltd.