1 引言

數(shù)據(jù)采集系統(tǒng)常需要進(jìn)行異步串行數(shù)據(jù)傳輸。目前廣泛使用的RS232異步串行接口,如8250、 NS16450等專用集成器件,雖然使用簡單,卻占用電路板面積、布線復(fù)雜等缺點(diǎn)。片上系統(tǒng)SoC(System on Chip)是以嵌入式系統(tǒng)為核心,以IP復(fù)用技術(shù)為基礎(chǔ),集軟、硬件于一體的設(shè)計(jì)方法。使用IP復(fù)用技術(shù),將UART集成到FPGA器件上,可增加系統(tǒng)的可靠性,縮小PCB板面積;其次由于IP核的特點(diǎn),使用IP核可使整個系統(tǒng)更加靈活,還可根據(jù)需要實(shí)現(xiàn)功能升級、擴(kuò)充和裁減。這里采用VHDL語言編寫 UART模塊,將其集成到FPGA上,與器件其他功能模塊構(gòu)成片上系統(tǒng)SoC。

2 異步串行口模塊設(shè)計(jì)與實(shí)現(xiàn)

2.1 UART結(jié)構(gòu)

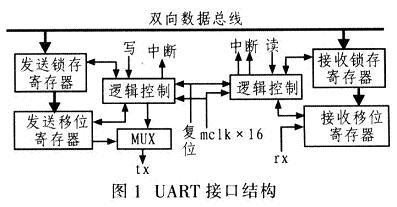

圖1為完整的UART接口,包括由發(fā)送鎖存器、發(fā)送移位寄存器和邏輯控制組成的發(fā)送模塊(txmit),以及由接收鎖存器、接收移位寄存器和邏輯控制組成的接收模塊(rxcver)。發(fā)送模塊和接收模塊除共用復(fù)位信號、時鐘信號和并行數(shù)據(jù)線外,各自分別有輸入輸出和邏輯控制單元。

2.2 UART的幀格式

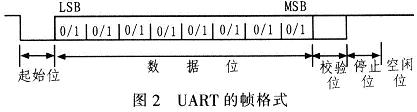

圖2為UART的幀格式。該幀格式包括線路空閑狀態(tài)(idie,高電平)、起始位 (start bit,低電平)、5~8位數(shù)據(jù)位(databit)、校驗(yàn)位(parity bit,可選)和停止位(stop bit,位數(shù)可為1、1.5、2位)。該格式是由起始位和停止位實(shí)現(xiàn)字符同步。UART內(nèi)部一般有配置寄存器,可配置數(shù)據(jù)位數(shù)(5~8位)、是否有校驗(yàn)位和校驗(yàn)的類型、停止位的位數(shù)等設(shè)置。

2.3 波特率時鐘的控制

由于數(shù)字量接口、工作模式選擇、實(shí)時監(jiān)測接口的波特率都不同,UART核包含一個可編程的波特率發(fā)生器,可靈活配置波特率。波特率發(fā)生器給發(fā)送模塊和接收模塊提供發(fā)送數(shù)據(jù)和接收數(shù)據(jù)的基準(zhǔn)時鐘,波特率發(fā)生器產(chǎn)生的時鐘mclkx16是串行數(shù)據(jù)波特率的16倍。它對系統(tǒng)時鐘n分頻,n=系統(tǒng)時鐘/波特率×16,針對不同波特率設(shè)定相應(yīng)數(shù)值可得到所期望的波特率時鐘。

2.4 發(fā)送模塊設(shè)計(jì)

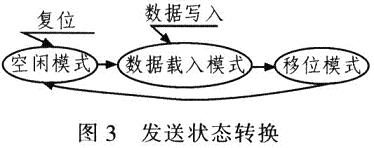

發(fā)送模塊分為空閑、載入數(shù)據(jù)、移位等3種模式。如圖3所示。當(dāng)并行8位數(shù)據(jù)從總線寫入發(fā)送模塊后,發(fā)送模塊將并行數(shù)據(jù)裝入鎖存器thr中,然后在移位寄存器tsr中將數(shù)據(jù)移位,產(chǎn)生完整的發(fā)送序列(包括起始位,數(shù)據(jù)位,奇偶校驗(yàn)位和停止位),以相應(yīng)波特率從tx發(fā)送。發(fā)送模塊的輸入時鐘mclkx16是串行數(shù)據(jù)波特率的16倍,模塊內(nèi)部將其16分頻后得到波特率時鐘txclk。

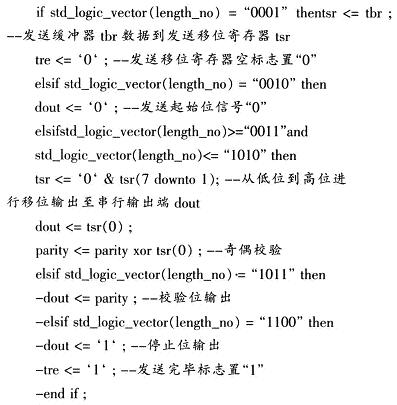

發(fā)送模塊部分VHDL程序如下:

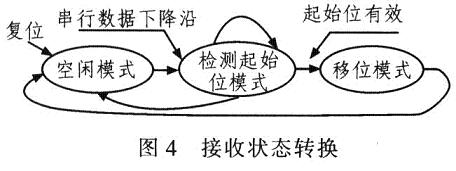

2.5 接收模塊設(shè)計(jì)

接收模塊也分為空閑、檢測起始位、移位等3種模式。如圖4所示。首先捕捉起始位,在 mclkx16時鐘下不斷檢測從rx端輸入數(shù)據(jù)的起始位,當(dāng)檢測到起始位后,接收模塊由空閑模式轉(zhuǎn)換為移位模式,并且16分頻mclkx16產(chǎn)生 rxclk波特率時鐘。此時rxclk時鐘的上升沿位于串行數(shù)據(jù)每一位的中間,這樣接下來的數(shù)據(jù)在每一位的中點(diǎn)采樣。然后由rxclk控制在上升沿將數(shù)據(jù)位寫入移位寄存器rgr的rsr[7]位,并且rsr右移1位,依次將8位數(shù)據(jù)全部寫入rsr,并且停止產(chǎn)生rxclk波特率時鐘。判斷奇偶校驗(yàn)、幀結(jié)構(gòu)和溢出標(biāo)志正確后,rsr寄存器中的數(shù)據(jù)寫入rhr數(shù)據(jù)鎖存寄存器中,最后由8位數(shù)據(jù)總線輸出轉(zhuǎn)換完成的數(shù)據(jù)。

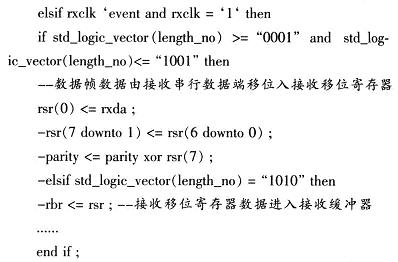

接收模塊部分VHDL程序如下:

3 硬件電路設(shè)計(jì)

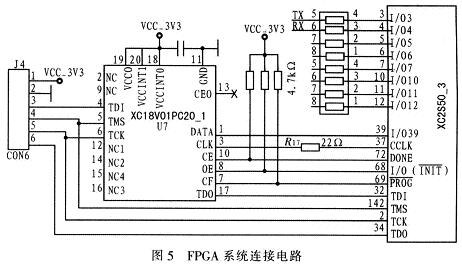

UART IP核設(shè)計(jì)完成后需要嵌入FPGA系統(tǒng)中才能運(yùn)行,該系統(tǒng)選用Xilinx公司Spartan-IIE XC2S50型FPGA和與其配套的EPROM XC18V01組成,如圖5所示。該系統(tǒng)已實(shí)現(xiàn)設(shè)計(jì)要求的功能,實(shí)現(xiàn)IP核的驗(yàn)證。

4 結(jié)果分析

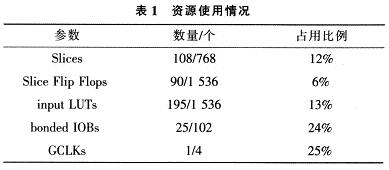

程序經(jīng)仿真驗(yàn)證后,須綜合生成IP核并嵌人FPGA中。使用Xilinx公司的Xilinx ISE工具綜合UART模塊,F(xiàn)PGA選用Xilinx公司Spartan-IIE XC2S50,系統(tǒng)時鐘40 MHz。經(jīng)Xil-inx ISE后,資源使用結(jié)果如表1所示。表明使用少量FPGA的Slice和LUT單元就可生成UART核,節(jié)省資源UART核可靈活分成接收和發(fā)送兩部分,可根據(jù)需要選擇使用。節(jié)省系統(tǒng)資源;一些控制標(biāo)志字也可根據(jù)需要自行刪減和擴(kuò)充。最后將集成有UART核的FPGA數(shù)據(jù)采集系統(tǒng)與測試臺進(jìn)行異步串行通信實(shí)驗(yàn),檢測通信數(shù)據(jù)表明使用UART核傳輸數(shù)據(jù)穩(wěn)定可靠。

5 結(jié)束語

數(shù)據(jù)采集系統(tǒng)經(jīng)常采用UART異步串行通信接口作為系統(tǒng)的短距離串行通信。相對于傳統(tǒng)的UART器件來說,把具有UART功能的IP核集成在FPGA中的更有利于提高數(shù)據(jù)采集系統(tǒng)的可靠性和穩(wěn)定性,減小電路板面積。該系統(tǒng)設(shè)計(jì)的UART IP核通過仿真驗(yàn)證,經(jīng)綜合、編譯、嵌入FPGA,成功實(shí)現(xiàn)系統(tǒng)通信。