隨著大規模和超大規模FPGA/CPLD器件的誕生和發展,以HDL(硬件描述語言)為工具、FPGA/CPLD器件為載體的EDA技術的應用越來越廣泛.從小型電子系統到大規模SOC(Systemonachip)設計,已經無處不在.在FPGA/CPLD設計中,狀態機是最典型、應用最廣泛的時序電路模塊,如何設計一個穩定可靠的狀態機是我們必須面對的問題.

1、狀態機的特點和常見問題

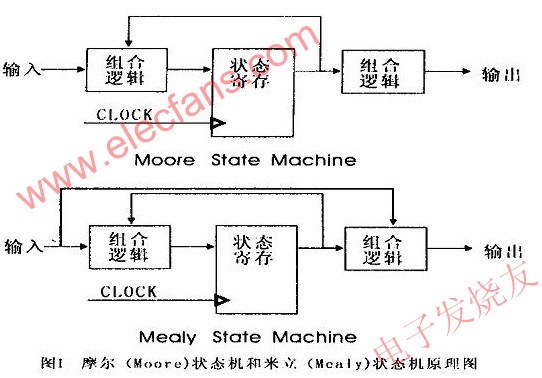

標準狀態機分為摩爾(Moore)狀態機和米立(Mealy)狀態機兩類.Moore狀態機的輸出僅與當前狀態值有關,且只在時鐘邊沿到來時才會有狀態變化.Mealy狀態機的輸出不僅與當前狀態值有關,而且與當前輸入值有關,這一特點使其控制和輸出更加靈活,但同時也增加了設計復雜程度.其原理如圖1所示.

根據圖1所示,很容易理解狀態機的結構.但是為什么要使用狀態機而不使用一般時序電路呢?這是因為它具有一些一般時序電路無法比擬的優點.

用VHDL描述的狀態機結構分明,易讀,易懂,易排錯;

相對其它時序電路而言,狀態機更加穩定,運行模式類似于CPU,易于實現順序控制等.

用VHDL語言描述狀態機屬于一種高層次建模,結果經常出現一些出乎設計者意外的情況:

在兩個狀態轉換時,出現過渡狀態.

在運行過程中,進入非法狀態.

在一種器件上綜合出理想結果,移植到另一器件上時,不能得到與之相符的結果.

狀態機能夠穩定工作,但占用邏輯資源過多.

在針對FPGA器件綜合時,這種情況出現的可能性更大.我們必須慎重設計狀態機,分析狀態機內在結構,在Moore狀態機中輸出信號是當前狀態值的譯碼,當狀態寄存器的狀態值穩定時,輸出也隨之穩定了.經綜合器綜合后一般生成以觸發器為核心的狀態寄存電路,其穩定性由此決定.如果CLOCK信號的上升沿到達各觸發器的時間嚴格一致的話,狀態值也會嚴格按照設計要求在規定的狀態值之間轉換.然而這只是一種理想情況,實際CPLD/FPGA器件一般無法滿足這種苛刻的時序要求,特別是在布線后這些觸發器相距較遠時,CLOCK到達各觸發器的延時往往有一些差異.這種差異將直接導致狀態機在狀態轉換時產生過渡狀態,當這種延時進一步加大時,將有可能導致狀態機進入非法狀態.這就是Moore狀態機的失效機理.對于Mealy狀態機而言,由于其任何時刻的輸出與輸入有關,這種情況就更常見了.

2 狀態機設計方案比較

2.1 采用枚舉數據類型定義狀態值

在設計中定義狀態機的狀態值為枚舉數據類型,綜合器一般把它表示為二進制數的序列,綜合后生成以觸發器為核心的狀態寄存電路,寄存器用量會減少,其綜合效率和電路速度將會在一定程度上得到提高.

例1 定義狀態值為枚舉類型的狀態機VHDL程序.

library ieee;

use ieee.std_logic_1164 all;

entity example is

port(clk:in std_logic;

mach_input:in std_logic;

mach_outputs:out std_logic_vector(0 to 1));

end example;

architecture behave of example is

type states is(st0,st1,st2,st3); --定義states為枚舉類型

signal current_state,next_state:states;

begin

state_change:process(clk) --狀態改變進程

begin

wait until clk'event and clk='1';

current_state<=next_state;

end process state_change;

combination:process(current_state,mach_input)

…… --輸出狀態值譯碼,給"next_state"賦新值.省略

end behave;

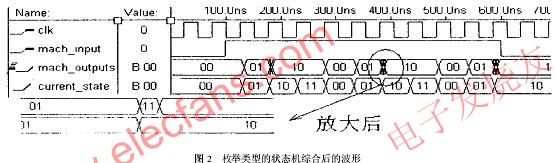

圖2 枚舉類型的狀態機綜合后的波形

例1是一個四狀態全編碼狀態機,綜合后的仿真波形如圖2所示.從放大后的局部可以看出輸出狀態值從“01”到“10”轉換過程中出現了過渡狀態“11”.從微觀上分析中間信號“Current_state”狀態轉換過程,狀態寄存器的高位翻轉和低位翻轉時間是不一致的,當高位翻轉速度快時,會產生過渡狀態“11”,當低位翻轉速度快時會產生過渡狀態“00”.若狀態機的狀態值更多的話,則產生過渡狀態的概率更大.如果在非全編碼狀態機中,由于這種過渡狀態的反饋作用,將直接導致電路進入非法狀態,若此時電路不具備自啟動功能,那么電路將無法返回正常工作狀態.

因為狀態機的輸出信號常用作重要的控制,如:三態使能,寄存器清零等.所以這種結果是不允許的,如何消除此類過渡狀態呢?方法之一是采用格雷碼表示狀態值.

2.2 用格雷碼表示狀態值

格雷碼的特點是任意相鄰兩個數據之間只有一位不同,這一特點使得采用格雷碼表示狀態值的狀態機,可以在很大程度上消除由延時引起的過渡狀態.將例1改進之后的程序如例2.

例2 采用格雷碼表示狀態值的狀態機.

library ieee;

use ieee.std_logic_1164 all;

entity example is

port(clk:in std_logic;

mach_input:in std_logic;

mach_outputs:out std_logic_vector(0 to 1));

end example;

architecture behave of example is

constant st0:std_logic_vector(0 to 1):="00";

constant st1 :std_logic_vector(0 to 1):="01";

constant st2:std_logic_vector(0 to 1):="11";

constant st3:std_logic_vector(0 to 1):="10";

signal current_state,next_state:std_logic

vector(0to1);

begin

……

endbebave;

采用該方法,寄存器的狀態在相鄰狀態之間跳轉時,只有一位變化,產生過渡狀態的概率大大降低.但是當一個狀態到下一個狀態有多種轉換路徑時,就不能保證狀態跳轉時只有一位變化,這樣將無法發揮格雷碼的特點.

2.3 定義“ONEHOT”風格的狀態值編碼

雖然VHDL語言的目標之一是遠離硬件,但是到目前為止并沒有完全實現,所以VHDL程序在針對不同的器件綜合時,仍然會有很大差異.特別是FPGA器件,當我們采用格雷表示狀態值,描述一個簡單的狀態機時,就可能出現不穩定結果.在針對FPGA器件寫程序時,我們可以將狀態值定義為“ONEHOT”風格的狀態碼,將上例稍作修改,見例3.

例3 采用“ONEHOT”編碼的狀態機

library ieee;

use ieee std_logic_1164.all;

entity example is

port(clk:in std_logic;

mach_input:in std_logic;

mach_outputs:out std_logic_vector(0 to 1));

endexample;

architecture behave of example is

constant st0:std_logic_vector(0 to 3):="0001";

constant st1:std_logic_vector(0 to 3):="0010";

constant st2:std_logic_vector(0 to 3):="0100";

constant st3:std_logic_vector(0 to 3):="1000";

signal current_state,next_state:std_logic vector(0 to 3);

begin

……

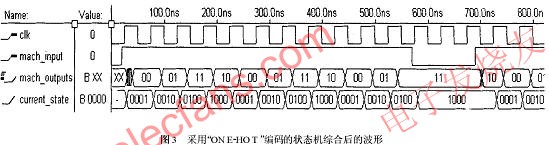

對FLEX10K系列器件綜合后的仿真結果如圖3所示.

圖3 采用“ONEHOT”編碼的狀態機綜合后的波形

如圖3所示,在輸入信號穩定以后,狀態機的輸出信號也穩定下來,定義這種風格的狀態碼來設計基于FPGA的狀態機是一種不錯的選擇.

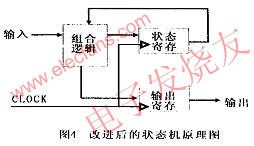

然而在輸入信號跳變時,電路還是會出現不穩定現象.此時我們已不能只從狀態值編碼方式尋找解決方法.回頭看看狀態機的原理框圖不難發現:狀態寄存器的輸出值是必須符合建立保持時間約束關系的.在上述狀態機中雖然采用了各種不同的編碼方式但都不能徹底消除這種過渡狀態,我們將電路結構稍作改進,一種更好的結構如圖4所示.這種結構的狀態機可有效抑制過渡狀態的出現.這是因為輸出寄存器只要求狀態值在時鐘的邊沿穩定.將上述程序改進之后的程序如圖4.

……

architecture behave of example1is

type states is(st0,st1,st2,st3); 定義states為枚舉類型

signal current_state,next_state:states;

signal temp:std_logic_vector(0 to 1); 定義一個信號用于引入輸出寄存器

begin

state_change:process(clk) --狀態改變進程

begin

wait until clk'eventandclk='1';

current_state<=next_state;

mach_outputs<=temp;

end process state_change;

……

圖5 改進后的狀態機綜合后的波形

顯然這種結構的狀態機穩定性優于一般結構的狀態機,但是它占用的邏輯資源更多,電路的速度可能下降,在設計時應綜合考慮.

另外,為防止電路進入非法狀態,可以設計成自啟動結構,在VHDL描述的狀態機中添加一個“when others”語句是行之有效的.

3 選擇不同編碼方式、不同結構的狀態機的技巧

3.1 針對不同結構器件選擇不同編碼風格

基于乘積項結構的CPLD器件適合于設計全編碼狀態機,在全編碼狀態機中采用格雷碼表示狀態值.這對于邏輯資源較少的器件是一種不錯的優化方法.

基于查找表結構的FPGA器件適合于設計成“ONEHOT”方式編碼的狀態機,這種結構狀態機只用一位二進制數表示一個狀態,可提高穩定性,但要占用更多的邏輯資源.

3.2 根據邏輯資源大小選擇狀態機結構

當設計的狀態機狀態轉換次序出現多路徑時,采用格雷碼表示狀態值不會有任何作用,因為此時有些相鄰狀態不只是一位不同.在邏輯資源允許的情況下,可以考慮在狀態機后級增加一級輸出寄存器,可確保輸出不產生毛刺,使狀態機輸出穩定可靠的信號.