作為賽靈思用戶論壇的定期訪客,我注意到新用戶往往對時序收斂以及如何使用時序約束來達(dá)到時序收斂感到困惑。為幫助 FPGA設(shè)計新手實現(xiàn)時序收斂,讓我們來深入了解時序約束以及如何利用時序約束實現(xiàn)FPGA 設(shè)計的最優(yōu)結(jié)果。

何為時序約束?

為保證設(shè)計的成功,設(shè)計人員必須確保設(shè)計能在特定時限內(nèi)完成指定任務(wù)。要實現(xiàn)這個目的,我們可將時序約束應(yīng)用于連線中——從某 FPGA 元件到 FPGA 內(nèi)部或 FPGA 所在 PCB 上后續(xù)元件輸入的一條或多條路徑。

在 FPGA 設(shè)計中主要有四種類型的時序約束:PERIOD、OFFSET IN、OFFSET OUT 以及 FROM: TO(多周期)約束。

PERIOD 約束與建組

每個同步設(shè)計要有至少一個PERIOD 約束(時鐘周期規(guī)格),這是最基本的約束類型,指定了時鐘周期及其占空比。若設(shè)計中有不止一個時鐘,則每個時鐘都有自己的 PERIOD 約束。PERIOD約束決定了我們?nèi)绾芜M(jìn)行布線,來滿足設(shè)計正常工作的時序要求。

為簡化時序約束應(yīng)用過程,常常可將具有類似屬性的連線分組為一組總線或一組控制線。這樣做有助于完成正確為設(shè)計約束定義優(yōu)先級這一關(guān)鍵步驟。

設(shè)計約束優(yōu)先次序排列

若設(shè)計有多重約束,則需進(jìn)行優(yōu)先次序排列。一般來說,約束的一般性越強(qiáng),其優(yōu)先級越低。相反,約束的針對性越強(qiáng),其優(yōu)先級越高。舉例來說,時鐘網(wǎng)絡(luò)上的某個一般性 PERIOD 約束將被特定網(wǎng)絡(luò)的具有更高優(yōu)先級的 FROM: TO 約束所覆蓋。

特定 FROM: TO(或 FROM: THRU:TO)約束在時鐘域內(nèi)任意網(wǎng)絡(luò)中的重要性均高于一般性約束。

為便于進(jìn)行約束的優(yōu)先級排列,可運行賽靈思時序分析器(ISE® Design Suite中的靜態(tài)時序分析工具),并生成時序規(guī)格迭代報告,即常說的 .tsi 報告。該報告說明了各約束間是如何迭代的,以及該工具如何為各約束設(shè)置默認(rèn)優(yōu)先級。

采用 PRIORITY 約束關(guān)鍵詞可手動設(shè)置任一時序約束的優(yōu)先級并使其優(yōu)先于默認(rèn)的或預(yù)先設(shè)定的優(yōu)先級。這對同一路徑上的兩個或多個時序約束發(fā)生沖突時尤為有用。這里的優(yōu)先級指的是同一路徑上有兩個或多個時序約束時,該應(yīng)用哪一個。其余的低優(yōu)先級約束則被忽略。優(yōu)先級可在 -10 ~ +10 的范圍內(nèi)設(shè)置。

PRIORITY 值越低,優(yōu)先級越高。注意該值不會影響到哪些路徑應(yīng)率先布局和走線,只有當(dāng)優(yōu)先級相同的兩個約束出現(xiàn)在同一路徑上時,它才會影響由哪個約束控制該路徑。

下面將以 PERIOD 只控制從同步元件到同步元件之間的網(wǎng)絡(luò),如 FFS 到FFS 為例來進(jìn)一步介紹(約束以藍(lán)色顯示如下):

創(chuàng)建名為 tnm_clk20 的 TIMEGRP(時序分組),包含網(wǎng)絡(luò) clk20 驅(qū)動的所有下游同步組件。這些同步元件間的所有路徑均受時序規(guī)格“TS_clk20: 20ns”(同步元件到同步元件 20 納秒的時間要求)的約束。“HIGH 50%”指 clk20 的占空比為50/50。

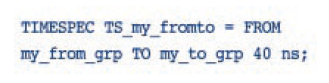

在第二個例子中,我們使用 FROM:TO 約束來定義對兩個分組間路徑的要求,即:

該命令的作用是告知工具,確保數(shù)據(jù)從時序分組“my_from_grp”包含的元件到“my_to_grp”的元件所用時間為 40納秒。時序分析器仍將計算從源分組到目標(biāo)分組的時鐘偏移,不過若時鐘關(guān)聯(lián),則優(yōu)先級較低。也可使用如下預(yù)定義分組:

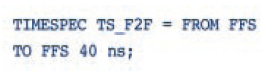

若不選定時間單位(納秒、皮秒等),則工具將自動默認(rèn)為納秒。例如,可這樣寫約束:

也可只寫From 或 只寫To ,以使其更具一般性:

如前所述,工具將自動默認(rèn)上文所述所有 FROM: TO 約束的優(yōu)先級高于PERIOD 約束,除非另有規(guī)定。

詳細(xì)查看 .tsi 報告

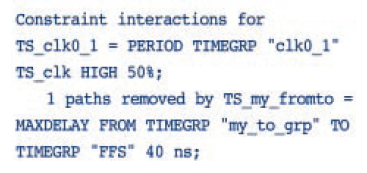

除幫助查看時序約束迭代外,.tsi 報告還就如何改進(jìn)通用約束文件 (UCF) 中的約束提供方法建議。該報告還會告知是否有路徑受多重時鐘域的約束。下面是約束迭代報告的例子:

在本例中,高優(yōu)先級的 FROM: TO約束(僅一個)將優(yōu)先于 PERIOD 約束應(yīng)用。

建立和保持

在實際的同步數(shù)字系統(tǒng)中,數(shù)據(jù)必須先于進(jìn)行采樣的時鐘脈沖邊沿到達(dá)。達(dá)到這一目標(biāo)所需的最短時間稱為“建立時間”。除了先于時鐘脈沖邊沿到達(dá)外,數(shù)據(jù)必須在時鐘脈沖邊沿保持一定時間,這一時間稱為“保持時間”。保持時間可

以為負(fù),此時數(shù)據(jù)在時鐘脈沖邊沿到達(dá)前便已結(jié)束;可以為零,此時數(shù)據(jù)保持到時鐘脈沖邊沿采樣;也可為正,此時數(shù)據(jù)保持到時鐘脈沖邊沿采樣完畢后一段時間。

根據(jù)設(shè)計,在 FPGA 架構(gòu)中,對所有速度等級,保持時間均不為正(或零或負(fù))。這樣可簡化布局和布線,因數(shù)據(jù)只

需先于時鐘脈沖邊沿到達(dá),并可在時鐘脈沖邊沿采樣發(fā)生后即刻發(fā)生變化。數(shù)據(jù)超出最小建立時間的值稱為時序裕量。時序裕量應(yīng)總是為正。若報告上出現(xiàn)時序裕量負(fù)值,則說明建立時序尚未得到充分滿足,數(shù)據(jù)到達(dá)太遲。

時鐘路徑本身也有延遲或偏移。因此,要分析時序,工具需計算出數(shù)據(jù)和時鐘到達(dá)所分析觸發(fā)器的時間。

約束違例的簡便補(bǔ)救辦法

重申一下:PERIOD 約束定義的是觸發(fā)器等同步元件的時鐘周期。可使用時序分析器來驗證同步元件之間的所有路徑是否滿足設(shè)計的建立和保持時序要求。PERIOD 約束違例將以負(fù)的時序裕量顯示在在時序報告,并說明到底是建立時間還是保持時間要求出現(xiàn)違例。所以若報告顯示發(fā)生了建立時間違例時該作何處理?應(yīng)找出兩個所分析的同步元件間一條較快路徑,或至少是某種方法來確保數(shù)據(jù)在合適時間內(nèi)到達(dá)并保持足夠長的時間,以便時鐘脈沖邊沿能夠正確采樣。若布局布線軟件無法找到更快的路徑,則可從 FPGA Editor 工具中手動進(jìn)行布線。

不過這是最后的手段。在弄清楚不用它如何解決問題之前,請盡量不要使用這種方法。只使用 FPGA Editor 查看底層結(jié)構(gòu)“知其所以然”,了解工具對設(shè)計的所做的處理,以達(dá)到讓設(shè)計恰當(dāng)?shù)氖褂肍PGA 資源來實現(xiàn)的目的。首先試試重構(gòu)電路來滿足設(shè)計的時序要求。一個比較簡單的方法就是在路徑上及早布置一個觸發(fā)器。該技術(shù)即為流水線,它會增加信號的延遲,不過也可使信號值得到正確地采樣。

若出現(xiàn)保持時間違例(數(shù)據(jù)在時鐘脈沖邊沿到來之前便已結(jié)束),則往往說明存在設(shè)計問題(架構(gòu)不良)。數(shù)值只能

在時鐘脈沖邊沿發(fā)生變化,而不是之前。

若外部信號值在時鐘脈沖邊沿之前發(fā)生變化,則需使用 DCM 或 PLL 延遲時鐘脈沖邊沿,這樣數(shù)據(jù)才能由新的延遲時鐘正確采樣。

有一種替代方法,就是在輸入/ 輸出模塊中使用 IDELAY 元件,將數(shù)據(jù)移到時鐘有效的位置上。

數(shù)據(jù)有效窗口與亞穩(wěn)態(tài)時鐘脈沖邊沿之前的時間(建立)加上時鐘脈沖邊沿之后的時間(保持)即為“數(shù)據(jù)有效窗口”,也就是數(shù)據(jù)保持穩(wěn)定,以進(jìn)行正常采樣的時間。若數(shù)據(jù)在此期間沒有保持有效,則結(jié)果存在不確定性,或不可知。

不過,數(shù)據(jù)的有效時間未達(dá)到規(guī)定的長度,并不意味著觸發(fā)器輸出為亞穩(wěn)態(tài)。亞穩(wěn)態(tài)不同于不確定。若不能滿足時序要求,則輸出可能為隨機(jī)的 1 或 0。亞穩(wěn)態(tài)是指時鐘脈沖邊沿“幾乎”能進(jìn)行狀態(tài)采集,而觸發(fā)器輸出則在時鐘脈沖邊沿之后的一段時間內(nèi)處于某種中間狀態(tài)(非 1 非 0)。亞穩(wěn)態(tài)無法避免,因其為時鐘脈沖邊沿和數(shù)據(jù)幾乎完全“錯過”時的電路物理狀態(tài)。

在設(shè)計合理的同步系統(tǒng)中,亞穩(wěn)態(tài)不是什么問題。當(dāng)出現(xiàn)異步情況(如敲擊鍵盤上的一個鍵)或當(dāng)兩個同步時鐘彼此異步時,亞穩(wěn)態(tài)就會成為問題。一般而言,若出現(xiàn)異步情況,則需進(jìn)行同步處理。

關(guān)于如何處理亞穩(wěn)態(tài)的情況,這里有篇不錯的專題文章: http://www.stanford.edu/class/ee183/handouts_

spr2003/synchronization_pres.pdf 。(要深入了解亞穩(wěn)態(tài),請查看本期第二篇文章 FPGA101)

傳輸時間與 OFFSET 約束

信號從 A 點到達(dá) B 點所用的時間稱為傳輸時間。它取決于傳輸介質(zhì)中光傳播的速度。例如,PCB 電路板上的走線以 6~7 皮秒/ 毫米來傳輸信號。可采用多種方法來確定這一時間值,例如進(jìn)行仿真,或在材料介電常數(shù)與走線幾何結(jié)構(gòu)已知的情況下,列方程求解。在芯片內(nèi),信號的行為方式也很類似,不過也會因通過緩存器、反相器、邏輯和互聯(lián)等有

源電路而發(fā)生延遲。

傳輸時間是可測量的,通常用示波器來測量。當(dāng)路徑上無有源元件時,傳輸時間一般不會有太大變化。若路徑在芯片內(nèi),則晶體管的作用會使路徑延遲在最大值與最小值之間變化。設(shè)計需同時滿足二者的時序要求。

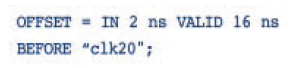

為告訴工具數(shù)據(jù)何時到達(dá)特定位置,需使用另一種名為“OFFSET_IN”的約束。“OFFSET_IN”約束在時鐘和數(shù)據(jù)進(jìn)入器件時,對其關(guān)系進(jìn)行了定義。以如下約束為例:

該約束告知工具,數(shù)據(jù)將在 clk20 脈沖上升沿之前 2 納秒建立在 PAD 上,并在到達(dá)后 16 納秒內(nèi)保持有效。該約束只對那些進(jìn)入由 clk20 或其衍生(衍生約束)提供時鐘的寄存器的 PAD 有效。

OFFSET 要求在 clk20 上有一個PERIOD 約束,這樣才能理解時鐘結(jié)構(gòu)。如下這樣也可接受:

不過,該約束不會檢查保持時間,因不清楚數(shù)據(jù)何時會從 FPGA 的引腳結(jié)束。若數(shù)據(jù)在時鐘脈沖邊沿 2 納秒之后才建立,則使用如下方案:

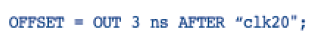

OFFSET_IN 適用于進(jìn)入器件的時鐘與數(shù)據(jù)之間的關(guān)系,另一種常見的OFFSET_OUT 約束定義時鐘在 FPGA 輸入處發(fā)生跳變后數(shù)據(jù)離開器件所需的時間。以下為常見的 OFFSET_OUT 用法:

該約束告知工具,需確保輸入時鐘在 FPGA 輸入跳變后 3 納秒時長后,數(shù)據(jù)出現(xiàn)在 FPGA 的輸出引腳上。該約束僅應(yīng)用于由 clk20 或其衍生(衍生約束)提供時鐘的寄存器驅(qū)動的 PAD。OFFSET 要求在 clk20 上有 PERIOD 約束,這樣才能理解時鐘結(jié)構(gòu)。保持時間不受 OFFSET_OUT 的約束。

若需要數(shù)據(jù)在時鐘脈沖邊沿前 2 納秒到達(dá)FPGA 輸出,則使用:

分組與分組名稱

時間分組是用來識別對于同步元件間的路徑集或連線集的約束的一種方式。向時序分組添加組件,應(yīng)使用 TNM、TNM_NET 或 TIMEGRP。

通過定義分組并給定分組之間的時序要求,可對路徑進(jìn)行約束。部分約束不需要時序分組,如 NET MAXDELAY。這一最大延遲 (MAXDELAY) 屬性定義了一條連線上允許的最大延遲。

時序名稱

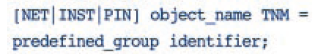

向用戶定義的分組添加組件,可這樣處理:

在此,“TNM”為保留字,用于定義時序分組的名稱。

在這種情況下,object_name 為帶分組元件或信號的名稱,predefined_group 為可選關(guān)鍵詞,標(biāo)示符可以是字母、數(shù)字和下劃線的任意組合。不能使用諸如 FFS、LATCHES 或RAMS 這樣的保留字。該變量對大小寫敏感。(TNM=abc 不等于 TNM=ABC)。

可將 TNM 應(yīng)用于任何連線、元件引腳、原語或宏。組件可加入一個以上的分組。例如,my_ffs_group TNM 中可含有 my_ff組件。同樣,my_ffs_group2 TNM 也可包含 my_ff 組件。要創(chuàng)建分組,請使用:

為時序目的,可在分組中包含任何關(guān)鍵詞元件。在本例中,NET CLOCK可追溯到觸發(fā)器 (FFS)。這些觸發(fā)器使用名稱 clk_group 進(jìn)行時序命名 (TNM)。然后,clk_group 就可以在TIMESPECS中使用了。也可使用實例創(chuàng)建分組,如:

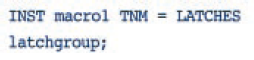

在 macro1 宏中的所有 LATCHES都放在名為 latchgroup 的分組中。類似的,在約束“INST mymac TNM=RAMS memories”中,所有 mymac 宏中的RAMS 都將放在稱為 memories 的分組中。且在以下約束中:

所有在 t e s t e r 宏中的 PADS、LATCHES、RAMS 及 FFS 都將放在名為 coverall 的分組中。相關(guān)的約束指南將包含完整的預(yù)定義分組列表。

簡潔至上

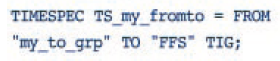

一般而言,約束的數(shù)量越少越好。復(fù)雜的約束引發(fā)的問題往往比解決的要多。另外,部分路徑或網(wǎng)絡(luò)是非關(guān)鍵性的,可對這些網(wǎng)絡(luò)不使用約束。TIG(時序忽略)約束用于清除對無需關(guān)注的路徑,或從虛假路徑上移除約束。以下為常見 TIG:

這條約束告知工具無需約束該路徑。這條的作用很重要,它可使工具不必在不關(guān)注的路徑上花費精力去滿足時序要求。在時序約束時忽略此路徑可縮短工具運行時間,提升所關(guān)注的路徑上的時序質(zhì)量。也可搭配“FROM: TO”約束來使用“TIG”,如下所示:

賽靈思有大量寶貴的關(guān)于時序約束的資源,其中最值得一讀的,我已在以下參考文獻(xiàn)中列出。若您有更深入的問題,請隨時與我聯(lián)系。我邀請您參加賽靈思社區(qū)論壇,該論壇可為 您的一些FPGA 設(shè)計中最棘手的問題提供充分的解答。

參考文獻(xiàn):

《約束指南》:UCF、PCF、HDL 約束語法, http://www.xilinx.com/support/documentation/sw_manuals/xilinx11/

cgd.pdf 。

《時序約束用戶指南》:如何約束設(shè)計的概念信息, http://www.xilinx.com/support/documentation/sw_manuals/xilinx11/ug612.pdf 。