摘要:為了使基于FPGA設(shè)計(jì)的信號處理系統(tǒng)具有更高運(yùn)行速度和具有更優(yōu)化的電路版圖布局布線,提出了一種適用于FPGA結(jié)構(gòu)的改進(jìn)型WALLACE TREE架構(gòu)乘法器。首先討論了基于標(biāo)準(zhǔn)單元3:2壓縮器的改進(jìn)型6:4壓縮器,根據(jù)FPGA中slice的結(jié)構(gòu)特點(diǎn)通過在FPGA Editer軟件工具編輯,對該壓縮器進(jìn)行邏輯優(yōu)化,將其應(yīng)用于FPGA的基本單元slice結(jié)構(gòu)中。并對乘法器的其他部分結(jié)構(gòu)優(yōu)化整合,實(shí)現(xiàn)一個資源和性能達(dá)到合理平衡,且易于在FPGA中實(shí)現(xiàn)的乘法器。實(shí)際運(yùn)行結(jié)果表明,該乘法器的關(guān)鍵路徑延時小于8.4 ns,使乘法器時鐘頻率和系統(tǒng)性能都得到很大提高。

關(guān)鍵詞:乘法器;WALLACE;FPGA;6:4壓縮器

在數(shù)字信號處理中,乘法器是整個硬件電路時序的關(guān)鍵路徑。速度和面積的優(yōu)化是乘法器設(shè)計(jì)過程的兩個主要考慮因素。由于現(xiàn)代可編程邏輯芯片F(xiàn)PGA的集成度越來越高,及其相對于ASIC設(shè)計(jì)難度較低和產(chǎn)品設(shè)計(jì)周期短,受到很多廠家和研究機(jī)構(gòu)的關(guān)注。利用它的可編程和可擴(kuò)展性,可將傳統(tǒng)乘法器設(shè)計(jì)方法應(yīng)用到FPGA芯片中。乘法器設(shè)計(jì)基本上是部分積的生成及其之間的相加的優(yōu)化過程。針對FPGA內(nèi)部固有結(jié)構(gòu)的特點(diǎn),本文著重介紹了一種基于WALLACETREE優(yōu)化算法的改進(jìn)型乘法器架構(gòu)。根據(jù)FPGA內(nèi)部標(biāo)準(zhǔn)獨(dú)特slice單元,有必要對WALLACE TREE部分單元加以研究優(yōu)化,從而讓在FPGA的乘法器設(shè)計(jì)中的關(guān)鍵路徑時延得以減小,整體時鐘性能得以提高。也能夠使FPGA的面積資源合理優(yōu)化,提高器件的整體資源利用率。

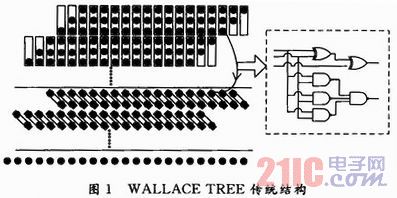

1 WALLACE TREE結(jié)構(gòu)

WALLACE TREE是對部分積規(guī)約,減小乘法器關(guān)鍵路徑時延的一種算法。傳統(tǒng)WALLACE TREE結(jié)構(gòu)的CSA(Carry Save Adder)陣列乘法器如圖1所示,其中“·”代表生成的多個部分乘積項(xiàng),相應(yīng)電路中用邏輯與門來實(shí)現(xiàn)。求和陣列將前面生成的多個部分積通過3:2 CSA壓縮器,將其壓縮成2個部分積,最后通過末級進(jìn)位相加得到所需的最終乘積結(jié)果。圖中矩形框所示為3:2 CSA壓縮器,其電路邏輯等效于一個全加器結(jié)構(gòu)。通過運(yùn)算可知N個部分積,要經(jīng)類似的log(2N/3)級3:2壓縮,就可得到2個部分積。

2 壓縮器的優(yōu)化

由于FPGA內(nèi)部的結(jié)構(gòu)是固定的,沒有以上WALLACE TREE所需要的CSA標(biāo)準(zhǔn)全加器結(jié)構(gòu)。因此,在傳統(tǒng)的FPGA電路綜合實(shí)現(xiàn)時,該CSA全加

器被綜合在FPGA內(nèi)部查找表(LUT)和進(jìn)位鏈中,占用了整個slice單元的資源。由于經(jīng)典WALLACETREE結(jié)構(gòu)不具有良好的對稱性且需要權(quán)重對齊等因素,勢必要增大FPGA電路的復(fù)雜度,增加大量的FPGA內(nèi)部布局和布線資源,在FPGA中不規(guī)則的布局布線結(jié)構(gòu),也增大了關(guān)鍵路徑的時延。

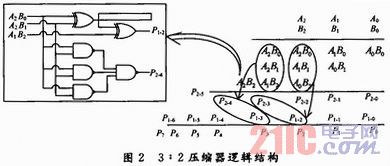

為在FPGA中較好地實(shí)現(xiàn)WALLACE TREE結(jié)構(gòu),結(jié)合FPGA中最小標(biāo)準(zhǔn)單元的結(jié)構(gòu)silce,對CSA全加器單元結(jié)構(gòu)加以改進(jìn)。如圖2所示,可將WALLACE TREE相鄰的平級3:2 CSA壓縮器合并成一個6:4壓縮器。該壓縮器只需使用1個FPGA的silce資源,就能實(shí)現(xiàn)其數(shù)字邏輯。下面以3×3乘法器為例,進(jìn)行WALLACE TREE壓縮器的推導(dǎo)和優(yōu)化。如圖2的第一個部分積,部分積低位空白應(yīng)補(bǔ)0,高位空白位用該部分積的最高位補(bǔ)齊。

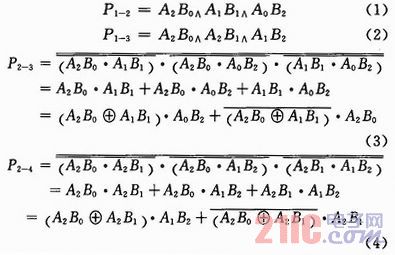

下面對2個3:2 CSA壓縮器合并成一個6:4壓縮器單元運(yùn)算邏輯做理論推導(dǎo),其中:

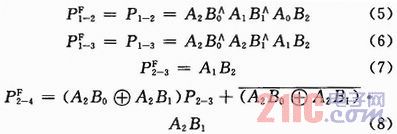

合并這兩項(xiàng)3:2壓縮為6:4壓縮時,A1B2和P23屬同級進(jìn)位,在計(jì)算過程中可將這兩項(xiàng)的位置互換,因此上式可推導(dǎo)演化成:

3 改進(jìn)CSA的FPGA實(shí)現(xiàn)

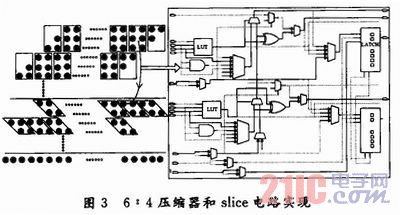

Xilinx提供了一項(xiàng)強(qiáng)大的用戶界面軟件工具FPGA Editer,可以通過手動編輯和修改FPGA最基本的標(biāo)準(zhǔn)單元slice結(jié)構(gòu),使其符合所需要的邏輯。圖3左邊是一個WALLACE TREE 6:4壓縮的整體結(jié)構(gòu),右邊是實(shí)現(xiàn)架構(gòu)中一個6:4壓縮的FPGA內(nèi)部標(biāo)準(zhǔn)單元slice。slice電路中虛線是器件原有的預(yù)布線,實(shí)線是根據(jù)實(shí)際電路邏輯手動編輯后slice內(nèi)部電路布線。根據(jù)上一面的推導(dǎo)式(5)~(8),slice內(nèi)部的2個查找表(LUT)單元被配置成2輸入異或門單元。為了使整體WALLACE TREE布線齊整,還將式(7)直通邏輯實(shí)現(xiàn)也在該級slice壓縮器中完成,其中輸入電平A1B2經(jīng)過2個MUX和一個配置為1的常有效LATCH輸出到,形成一個直通電路。

從圖3可以看出,WALLACE TREE的6:4壓縮器單元只用一個slice就可以實(shí)現(xiàn)。而幾乎所有Xilinx的FPGA器件內(nèi)部slice結(jié)構(gòu)都類似,因此該6:4壓縮器在基本的FPGA器件中都可以通過此手動編輯方法實(shí)現(xiàn),形成一個可供頂層WALLACETREE邏輯調(diào)用的硬宏模塊。

4 乘法器的FPGA實(shí)現(xiàn)和仿真

在頂層乘法器WALLACE TREE邏輯架構(gòu)設(shè)計(jì)中,可以通過描述語言模塊例化來調(diào)用前面手動實(shí)現(xiàn)的6:4壓縮器,可將slice壓縮模塊看成一個FPGA中固有的IP硬宏模塊,調(diào)用方法與使用FPGA器件內(nèi)部的其他IP沒有區(qū)別。在FPGA Editer中對各個模塊相互位置按樹的層次和數(shù)字邏輯順序進(jìn)行約束排列,形成一個約束文件。這樣FPGA芯片面積資源不僅得到充分的利用,在時序方面也會減小關(guān)鍵路徑的時延,提高時鐘頻率。

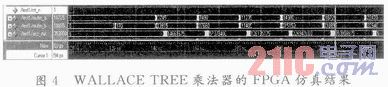

該乘法器的末級加法器要把WALLACE TREE得到的最后2個部分積快速的相加得到最終結(jié)果。末級加法器的實(shí)現(xiàn)方法有CPA(Carry Propaga tion Adder),該加法器的利用超前進(jìn)位,可以使進(jìn)位鏈這個關(guān)鍵路徑的時序在邏輯上層次減小。但該加法器在FPGA綜合實(shí)現(xiàn)后形成復(fù)雜結(jié)構(gòu),帶來的是利用了很大的布局面積和布線資源。FPGA內(nèi)部結(jié)構(gòu)中以其特有縱向結(jié)構(gòu)的超級進(jìn)位鏈,可將進(jìn)位的器件延時和布線延時優(yōu)化。可以利用該進(jìn)位鏈,合理進(jìn)行布局約束優(yōu)化,使進(jìn)位鏈路徑時序減小。實(shí)踐表明,在16×16的加法器中,該進(jìn)位鏈的時延只有6 ns左右,大大減小了整個乘法器關(guān)鍵路徑延時。在圖4中列出了本設(shè)計(jì)的FPGA布局布線布局布線后仿真結(jié)果。該結(jié)果在XILINX-Virtex5-VC5VSX35T器件中運(yùn)行,通過ModelSim仿真輸出采集。multin_a和multin_b分別是16位乘數(shù),acc_out是相乘后輸出的32位結(jié)果,rst_n是復(fù)位清0信號。整個設(shè)計(jì)的硬件描述語言采用Verelog語言,其中例化了預(yù)先用FPGA Editer工具設(shè)計(jì)好的6:4硬宏壓縮模塊。

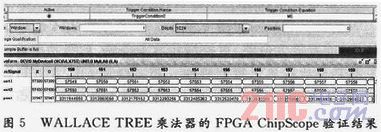

圖5給出了WALLACE TREE乘法器設(shè)計(jì)的XILLNX-Virtex5-VC5VSX35T器件實(shí)際運(yùn)行性能參數(shù)。該結(jié)果是FPGA器件以系統(tǒng)時鐘為120 MHz運(yùn)行時,通過XILLNX公司ISE套裝軟件ChipScope采集獲取的數(shù)據(jù)。圖中,unt1和unt2采用FPGA內(nèi)部一個測試計(jì)數(shù)器輸出的16位無符號乘數(shù),將其輸入WALLACE TREE乘法器運(yùn)算后,得到一組32位乘積結(jié)果。該實(shí)測結(jié)果表明,該結(jié)構(gòu)的乘法器能工作正常工作在120 MHz系統(tǒng)時鐘的條件下,其實(shí)現(xiàn)電路關(guān)鍵路徑的延時小于8.33ns。

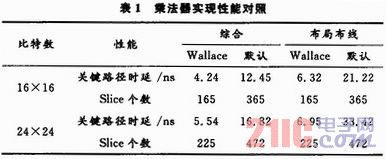

表1分別列出了16×16,24×24位乘法器在FPGA中用工具默認(rèn)方法和本文方法生成的資源和時序?qū)φ請D。可以看出,本文的結(jié)構(gòu)更合理,資源和速度都得到了一定程度的優(yōu)化。

5 結(jié)語

本文根據(jù)FPGA內(nèi)部標(biāo)準(zhǔn)單元結(jié)構(gòu),提出了一種改進(jìn)的WALLACE TREE 6:4壓縮器的新型邏輯結(jié)構(gòu),并用Xilinx提供的工具套件FPGA Edi-ter實(shí)現(xiàn)了該壓縮器單元。結(jié)合乘法器在FPGA中的仿真表明,該結(jié)構(gòu)的乘法器在提高系統(tǒng)的時鐘頻率和節(jié)省布局布線方面都有很大的優(yōu)勢。